MAGAZINE AN ONICONNECTOOT PUBLICATION

EMI: What It is, Where It **Comes From and How to** Control It p.10

A Small Leak Can Sink a **Great Ship: EMC Behavior** of Traces Crossing Split Planes, Part I p.20

Top 10 Key EMC Design Considerations p.42

EMI / EMC

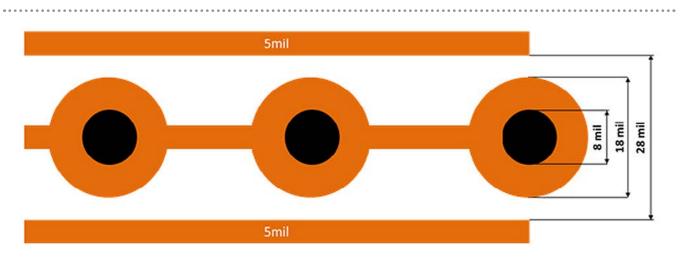

## THE best way to find a PCB fabricator, anywhere.

Quick Search

Advanced Search

Why did you choose THAT fabricator?

Designers: when you choose a fabricator, what guarantee do you have that they won't deliver scrap?

We can connect you with manufacturers that we have audited and are **qualified to deliver the product that you need**, on time and on budget.

### How we qualify PCB manufacturers

CLICK TO VIEW

(360) 531-3495 www.nextlevelpcb.com

### **FEATURED CONTENT**

Radiated emissions can cause a variety of problems on your PCB – even if you're designing boards with "mature" technologies. In this issue, our columnists and contributors tackle the challenges of achieving EMC and discuss some proven methods for minimizing EMI transmissions from the ground up.

### 10 EMI: What It is, Where It Comes From and How to Control It

by Lee Ritchey

20 A Small Leak Can Sink a Great Ship: EMC Behavior of Traces Crossing Split Planes, Part I by Ralf Bruening

42 Top 10 Key EMC Design Considerations

by Ashish Kumar & Pushek Madaan

**FEATURE COLUMN 32 Microwave Radiation Loss Concerns in PCBs** *by John Coonrod*

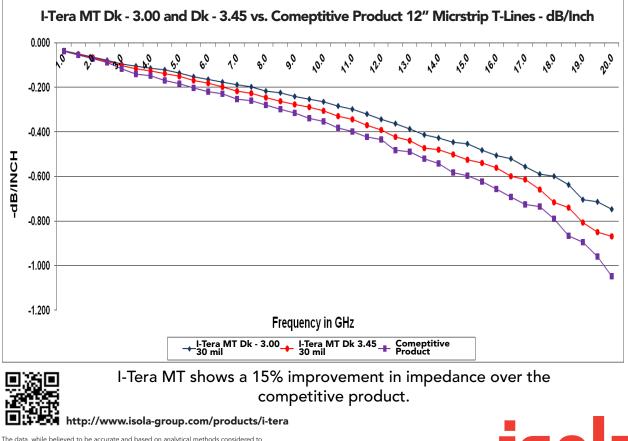

## The Next Generation High Speed Product from Isola

- Global constructions available in all regions

- Optimized constructions to improve lead free performance

- I-Speed delivers 15-20% lower insertion loss over competitive products through reduced copper roughness and dielectric loss

- Improved Z-axis CTE 2.70%

- I-Speed IPC 4101 Rev. C /21 /24 /121 /124 /129

- Offer spread and square weave glass styles (1035, 1067, 1078, 1086, 3313) for laminates and prepregs

- Minimizes micro-Dk effects of glass fabrics

- Enables the glass to absorb resin better and enhances CAF capabilities

- Improves yields at laser and mechanical drilling

- A low Df product with a low cost of ownership

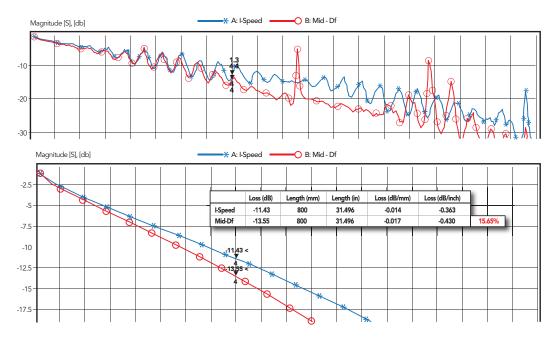

#### Effective Loss @ 4 GHz on a 32 inch line

I-Speed delivers 15-20% lower insertion loss over competitive low Df products.

http://www.isola-group.com/products/i-speed

The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these materials will be governed by the terms and conditions of the agreement under which they are sold.

Isola Group S.a.r.l. 3100 West Ray Rd., Suite 301, Chandler, AZ 85226 1-480-893-6527 http://www.isola-group.com

APRIL 2013

**VOLUME 2**

NUMBER 4

thepcbdesignmagazine.com

THE OPTIMUM MAGAZINE

DEDICATED TO

PCB DESIGN

MAGAZINE

## CONTENTS

#### ARTICLE

**54** Are Guard Traces Worth it? by Bert Simonovich

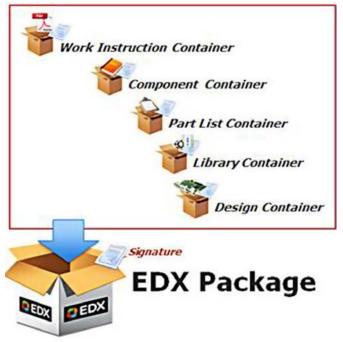

70 EDX: A New Standard for Sharing PCB IP by Jody Miller

#### **SHORTS**

- 53 DARPA Achieves Record Power Output

- 63 EDX Alliance Ensures PCB Design Data Transfer Security

#### TOP TEN MOST-READ NEWS

- **30** PCB007

- 35 Mil/Aero007

#### COLUMNS

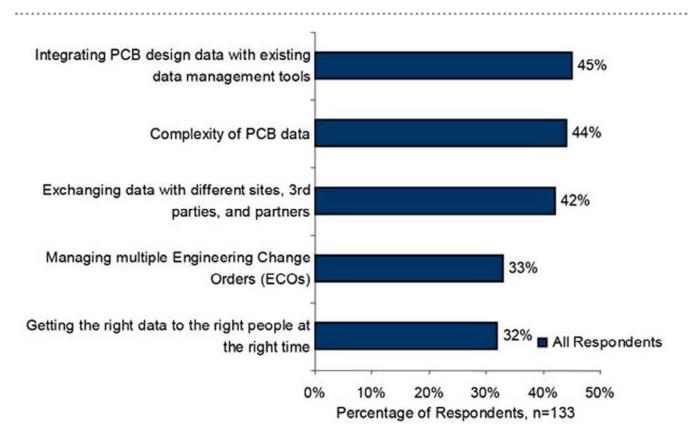

8 By The Numbers by Andy Shaughnessy

26 The Advantages of CAD by Jack Olson

**36 The Ten Commandments** of Design for Assembly by Amit Bahl

- 48 DesignCon: The Early Years by Istvan Novak

- 64 Electromagnetic Fields: Part 2 by Barry Olney

#### **VIDEO INTERVIEWS**

- 34 Lee Ritchey: Seeking the Limits of Materials

- 63 "Ask The Flexperts" Duo Informs, Entertains

- 69 Effective Modeling of PCB Structures

74 EMA Design Automation Ready for 2013 and Beyond

EXTRAS 78 Events Calendar

79 Advertiser Index & Masthead

# DYMAX CONFORMAL COATINGS. BETTER PROTECTION AND HIGHER THROUGHPUT. BEYOND A SHADOW OF A DOUBT.

Dymax Conformal Coatings cure in seconds with UV light – and with ambient moisture curing available for shadowed areas, you can be confident you're getting maximum protection – even underneath components. Add vivid blue fluorescing for easy inspection of coating coverage, and you'll see more throughput, in less time, using less floor space. All with unsurpassed protection against moisture, dust, chemicals, and temperature cycling. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. Visit **dymax.com/conformal**.

column

#### THE SHAUGHNESSY REPORT

# **By The Numbers**

#### by Andy Shaughnessy

I-CONNECT007

When I bought my first car that required monthly payments, my dad co-signed for the loan. The salesman tried some financial sleightof-hand, and then announced, "Figures don't lie." My dad, whose first new car was a 1949 Ford, answered, "Figures don't lie, but liars do figure."

Statistics, financial reports, unemployment rates – they're all open for interpretation.

For instance, the U.S. recently posted the March unemployment numbers. Unemploy-

ment fell to 7.6%, which is great news. Or is it? The percentage of able-bodied "potential" workers actually working is lower than any time in the last 34 years – 63%. People who give up on looking for a job don't count toward the final jobless head count. Still, a 7.6% unemployment rate is better than the 8-9% rates of a few years ago. But it all depends on whether you want to see good news or bad. I think any analysts or news anchors looking for causal relationships between these numbers and, say, an administration's economic policy may be trying to solve an equation with too many variables.

Worse, these monthly job reports don't tell us much specifically about those who design and manufacture electronics. It takes six months for the Bureau of Labor Statistics to break down various occupations' jobs data by geography, mean salary, etc.

Every so often I visit the <u>Bureau of Labor</u> <u>Statistics website</u>. I recently pored over the site, hoping to find some concrete, unambiguous jobs data regarding those who design or manufacture electronics. The BLS site has a cornucopia of interesting, cross-referenced data, if you know how to search for it. (Plus, I just like data and surveys. I even read the methodology behind polls used in political campaigns.)

The first problem: BLS has almost no concrete data about PCB design or designers. No matter how I searched, I found nothing about PCB designers, design engineers, or circuit engineers. We've all seen now how hard it is to quantify the number of PCB designers in the US or worldwide. Well, to the BLS, the entire PCB industry is nearly invisible. More accurately, the info is hidden in plain sight among larger industries, and delineated by final product

There was, however, a lot of data on electrical engineers; unfortunately, it includes EEs working at power plants and other careers not related to PCBs. But this will give us a good ballpark reference.

The May 2012 jobs data tells us that there were 160,560 EEs employed in the U.S. last spring. Their annual mean wage (found by add-ing the total salaries and dividing by the number of workers, in case you've blocked out everything you learned in your "sadistics" class) of \$91,810 is about what we'd expect.

There were 12,960 EEs involved in "Semiconductor, and Other Electronic Component Manufacturing," earning an annual mean wage of \$99,540. "Computer Systems Design and Related Services" totaled 4,520 EEs, earning an annual mean wage of \$102,860.

The states with the highest EE employment:

California – 24,110

Texas – 11,840

New York – 9,120

Massachusetts – 7,520

Florida – 7,270

The states paying the highest EE salaries:

- 1. California \$107,280

- 2. Alaska \$104,360

- 3. District of Columbia \$104,040

- 4. Massachusetts \$101,750

- 5. Rhode Island \$97,760

Not surprisingly, the states paying the highest salaries have among the highest costs of living in the U.S. Also not surprisingly, San Jose rang up the highest annual mean wage for a metro area, \$115,300, and the highest concentration of EE jobs – 6,920. Even after back-to-back recessions, Silicon Valley still employs more EEs than many states in the U.S. The No. 2 metro area for EE job concentration was Huntsville, Alabama, with 1,590, and No. 3 was the "Space Coast" area near Titusville, Florida, with 1,290.

Huntsville and the Space Coast both revolve around military contracts; it will be interesting to see if these areas lose EE jobs as a result of the sequestration. Sure, they're really just cutting the projected increase in government spending. But it would be foolish to think sequestration won't have an effect on PCB design and manufacturing down the road.

It's difficult to find concrete data for our industry, but I'd I recommend that everyone check out the Bureau of Labor Statistics site. Hopefully, there will be updated EE numbers soon. **PCBDESIGN**

Andy Shaughnessy is managing editor of *The PCB Design Magazine.* He has been covering PCB design for 13 years. He can be reached by clicking here. **ENI:** What It is, Where It Comes From and How to Control It

reature

by Lee Ritchey SPEEDING EDGE

SUMMARY: There are a variety of technical books that address EMI and EMC. However, none of them really gets down to the basics of where EMI comes from, what it really is, why it is an issue and what to do about it.

There seems to be a great deal of mystery surrounding EMI and EMC. I have a shelf full of books on the subject. Some of them are technically very good and at least three of them are so full of misinformation that their followers are more likely to have EMI problems than if they did nothing. Of the books that are technically very good, all describe at great length how to measure near field and far field emissions and how to calibrate measurement setups.

However, none of them really gets down to the basics of where EMI comes from, what it really is, why it is an issue and what to do about it.

Electromagnetic interference (EMI) is electromagnetic energy that escapes one product and interferes with another. This can happen in two ways. First, electromagnetic energy can be radiated into space because there is an accidental antenna extending from the product. Second, the energy can be conducted out of the power lines of the product and into the power terminals of another product.

Conducted EMI is measured in the band of frequencies from 150 KHz to 30 MHz and radiated EMI is measured in the band of frequencies from 30 MHz to 1 GHz or to 5x the highest clock frequency, whichever is higher.

Electromagnetic compatibility (EMC) refers to a product that has been designed so that it is not interfered with by other products as a result of electromagnetic radiation or conduction. In other words, noise in the form of electromagnetic radiation coming from another source that can cause a product to malfunction does not affect it.

#### **Understanding EMI**

Starting with radiated EMI, I find it easiest to understand this energy by looking at it as an unwanted radio link. The same mechanism that makes a radio transmitter and receiver pair work is in effect when there is an EMI problem. Looking at what is needed for a good radio link helps understand what needs to be done to eliminate an EMI problem.

There are two necessary elements in a good radio transmitter, which is what we have when a product is failing EMI tests. These are a source of RF energy (transmitter), and a radiating surface

# HIGH QUALITY ADVANCED TECHNOLOGY PCBS

At Streamline Circuits we support today's advanced technology chip requirements (.08 mm BGAs) while continuing to uphold the quality and reliability needed by the commercial, medical, aerospace and military industries.

Rigid / Rigid-Flex / ML Flex

50 Layers (11+ stacked vias)

9+Lamination Cycles (Blind & Buried)

STREAMLINE CIRCUITS 1410 Martin Ave. Santa Clara, CA 95050

# IPC 6012C Class 3 w/Copper Wrap 3.23 Mil Hole-to-Copper Flat Copper / Epoxy Filled Vias

### CALL TODAY: +1 (877) 264-0343

NAV

email: sales@streamlinecircuits.com www.streamlinecircuits.com 1.6 Mil Laser Vias

4 Mil Mechanical Drills

#### MIL-SPEC 55110 AS9100C • ISO9001

#### reature

#### EMI: WHAT IT IS, WHERE IT COMES FROM AND HOW TO CONTROL IT continues

(antenna). If I remove either one, the source of EMI or the radio signal is removed. Controlling EMI consists of eliminating either the source or the antenna.

The rule of thumb methods passed around the engineering community tend to focus on removing the source of EMI. These methods evolved in the 1980s, when the operating frequencies of products were well below the 30 MHz starting point for measuring EMI. At that time, occasionally ASICs would have speeds fast enough to generate noise in the 30 MHz to 1 GHz range. Inserting a ferrite bead in the power lead of such a device prevented it from operating fast enough to cause EMI. Such techniques focus on removing the source.

Modern electronics operate well above the 30 MHz starting point for measuring radiated EMI. As a result, suppressing EMI with ferrite beads and other similar methods by preventing circuits from operating at high frequencies is not a choice. This leaves only one alternative – eliminating accidental antennas.

There are many speculations about what can make a good antenna. One that is commonly passed around is that traces on outer layers of PCBs can cause EMI. It is easy to demonstrate that this is not so<sup>[1]</sup>. Antennae are bidirectional. This means that an antenna that is good at receiving is equally good at transmitting and vice versa. One way to demonstrate that antennas or traces close to planes don't work well as antennas is to take a handheld AM radio tuned to a weak station. Move it close to a sheet of metal such as the planes in a PCB. The signal will fade away, even though the antenna is still some distance from the plane.

# What Makes a Good Antenna for Radiating EMI?

Stated simply, things that make good antennas are objects that stick up above the PCB (e.g., PLCC lead frames and other elements that leave the PCB, such as unshielded wires going to mice and monitors, etc.). Things that don't make good antennas are things that don't stick up, such as traces on a PCB. Two PCBs joined by a connector, such as a DIMM connector, form a dipole antenna that works very well. PGAs and BGAs in sockets also make good antennas. Points to remember:

- A two-board set will usually behave as a dipole antenna.

- An unshielded wire leaving a Faraday cage will be an antenna.

- Connecting logic ground to a Faraday cage in more than one place often turns the cage into an antenna.

- A component lead frame protruding above a PCB is an antenna.

- Cutting ground planes can turn a PCB into a dipole antenna.

- Connecting plug-in module face plates to logic ground turns the faceplate into an antenna.

#### **Three Treatments of Antennas**

There are three ways to treat potential antennas. These include:

- Shield them when they leave the product.

- Place a low-pass filter in series with the antenna where it leaves the product.

- Place the product in a Faraday cage.

Placing a low-pass filter on a wire as it exits a product is an effective way to prevent noise from getting onto the wire. For a low-pass filter to be effective it needs to produce substantial attenuation from 30 MHz to 1 GHz. Such a filter will need to be made from very low-inductance capacitors in order to work across this range. The best capacitors for this purpose are formed from the planes of the PCB, and either fill in a signal layer or part of a plane borrowed for this purpose. Implied in the use of low-pass filters is the idea that the useful signals exiting the product on such a wire are well below the 30 MHz starting point for measuring EMI. The ferrite donuts surrounding the cables to displays and other peripherals are doing this low-pass filter job. On occasion, I have seen an EMI practitioner place a ferrite around a wire or cable, such as a USB port, where the useful signals are in the EMI band. This results in reducing EMI, but it also creates attenuation of the useful signal, sometimes to the point of causing a malfunction.

Shields on cables are a way to prevent a wire that leaves a product from becoming an anten-

# Is your PCB design software holding you back?

# Cut your design time using the latest technologies

ZUKEN

### **Try CADSTAR Extreme for free!**

Includes high-speed and signal integrity plus much more... zuken.com/trycadstar

# CADSTAR

Proven Expert Desktop PCB Design Solution

#### reature

#### EMI: WHAT IT IS, WHERE IT COMES FROM AND HOW TO CONTROL IT continues

na. If the product does not have a Faraday cage (a metallic enclosure that surrounds a product that radiates energy in the EMI band), the shield needs to be tied to the logic ground of the PCB from which it exits. If the product is surrounded by a Faraday cage, the shield needs to be tied to the Faraday cage at the point where the wire exits. Shields are extensions of Faraday cages.

The Faraday cage reflects this energy back into the product. It rarely absorbs it. This is the ultimate method for containing EMI. It is necessary when a system has multiple PCBs or when there are large components sticking up that can serve as antennas. It should be pointed out that the Faraday cage itself can serve as antenna if the error is made to connect logic ground to the Faraday cage (some erroneously call it "chassis ground") at more than one place. The most common error of this type is to tie logic ground to the Faraday cage at the backplane of a system, and then to tie logic ground to the faceplates of the plug-in cards. A clue that this has happened is detecting EMI at the "cracks." I often hear this described as EMI "leaking out" at the cracks or seams of the box.

The Faraday cage usually is made up of parts of the chassis, such as the sides of a card cage. Because of this, the term "chassis ground" is often used when discussing EMI containment. It is confusing to use such terms, as they can mislead people. I use the term Faraday cage only when discussing EMI and represent it with this symbol:

True, some parts of the chassis are used to form part of the Faraday cage, but the "chassis" is not the EMI containment vessel.

#### The Source of EMI Energy

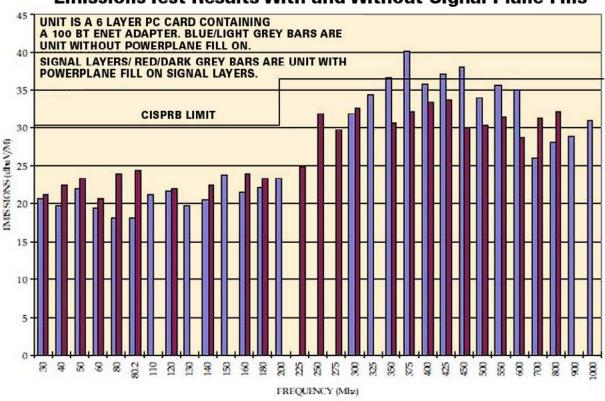

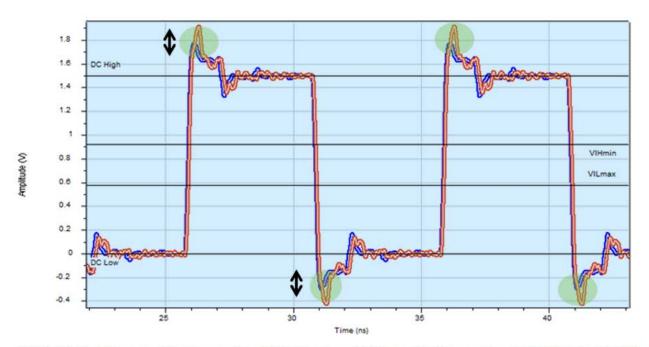

Traditional wisdom states that the system clock is the primary source of EMI. This was true long ago when the clock was the fastest signal in a product. However, this is not the case now and has not been so for quite some time. Figure 1 is the emissions spectrum for a dual-speed Ethernet interface card. The system clock is 33 MHz. None of the emissions in the spectrum are harmonics of the clock. Blue peaks are before adding plane capacitance and red peaks are after adding plane capacitance.

Notice that emissions are detected from about 30 MHz to over 1 GHz. Where are these signals coming from if not the clock? The answer is from ripple on Vcc due to inadequate bypassing. As can be seen from the paper by Todd Hubing<sup>[5]</sup>, switching frequencies above about 100 MHz cannot be supplied or contained by discrete bypass capacitors because of their parasitic inductance. The source of energy to support switching events above 100 MHz is the capacitance formed by the parallel power planes. In the above design, there was very little capacitance between the power planes. This was remedied by filling in unused space in signal layers to form additional plane capacitance. The result cited above was caused by this increase in plane capacitance. There is no other way to reduce emissions in the EMI frequency band to a level where this product would pass.

The energy involved in the above failure came from the fact that switching events attempted to draw current from a power subsystem incapable of delivering it. This resulted in an excessive ripple voltage on Vdd. Logic lines connected to logic 1 in CMOS circuits are essentially shorted to Vdd. Any ripple or noise voltage on Vdd is conducted out on the wire and can radiate into space.

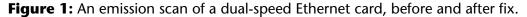

Figure 2 shows the switching voltage and current waveforms for a transmission line 12" long being driven by a 5 volt CMOS driver. The spectrum is a Fourier transform of the switching current waveform. Notice that this spectrum has frequency components from 85 MHz to about 900 MHz. The clock frequency is 30 MHz and there are no harmonics of the clock in this spectrum. If the power supply bypassing does not include sufficient plane capacitance to supply this current pulse, there will be a ripple voltage on Vdd that corresponds to it. This voltage waveform impressed on an antenna will result in emissions frequencies that match those

At U.S. Circuit, we had the vision to purpose-build our facility from the ground up with you, the customer, in mind. We invite you to step on in for a virtual tour of our state-of-the-art facility today. Welcome to U.S. Circuit!

U. S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 Ph: (760) 489-1413 Fax: (760) 489-2965 www.uscircuit.com

## Superior Quality Superior Service

Call for a Quote: (760) 489-1413 or email: rsojitra@uscircuit.com

ITAR Registered

ISO 9001:2008

MIL-PRF-55110G

#### reature

#### EMI: WHAT IT IS, WHERE IT COMES FROM AND HOW TO CONTROL IT continues

#### **Emissions Test Results With and Without Signal Plane Fills**

in the spectrum shown. Note: Todd Hubing's paper<sup>[5]</sup> demonstrates that plane capacitance is the supplier of current for frequencies above 100 MHz.

I have found that the best way to avoid EMI problems is by designing a bypassing scheme that minimizes ripple on Vdd. In fact, I have solved EMI problems, such as what is shown in Figure 1 by redesigning a PCB to improve the bypassing scheme. This involved adding enough plane capacitance to supply these high-frequency currents. Said another way, controlling EMI sources, ripple on Vdd being one of the biggest, is much less expensive than elaborate containment vessels. In the bargain, the circuits have better power sources and operate better.

#### **Conducted EMI**

Conducted EMI is energy that leaves a product through the power cord. The frequency spectrum of interest is 150 KHz to 30 MHz. This band of frequencies is well within the range of conventional components used to build lowpass filters such as inductors and capacitors. There is a wide range of such filters available for the manufacturers of DC-DC converters which can be inserted into the power lines as they enter or exit a product. For cost-sensitive products, it is often possible to build a low-pass filter from discrete components. In some cases, Ferrite torroids are clamped onto the power cord as it enters the product. This latter method is often found on low-cost products such as printers and monitors.

#### **Beware EMI Rules of Thumb**

A large body of information in circulation in the EMI community is flawed. I have watched some of these rules of thumb evolve when people who don't understand what really happens in high-speed circuits try to make up explanations for what is going on. This is the so called "it's magic" school of EMI control. In other cases, the rules appear to have been picked out of thin air.

#### EMI: WHAT IT IS, WHERE IT COMES FROM AND HOW TO CONTROL IT continues

Figure 2: Switching waveforms for a 12" transmission line with frequency spectrum.

When I encounter a proponent of such rules and ask for the underlying research or testing that validates those rules, the reply is often "well, everybody knows that," "I'm the EMI expert and you have to believe these rules until you prove them wrong," or, "if you don't follow these rules, I won't guarantee your product will pass EMI tests." All of these replies leave me with an unsatisfied feeling. I have done testing to check them out, and time and again they have turned out to be invalid. In some cases, the rules do no harm. In others, they have the potential to cause operational failures. References 1 through 4 below are papers that test several of these rules of thumb to see if they are valid. They are all available on the Speeding Edge web site (www.speedingedge.com). I strongly suggest you download and read them.

As part of the testing I have done on this topic, I have learned that it is easy to demonstrate that good EMI rules are valid. When the proponent of an EMI rule cannot demonstrate its validity, it is wise to be suspicious of it.

#### **Invalid EMI Rules**

The following EMI rules of thumb have been proven invalid:

$\bullet$  Right angle bends in signal traces cause  $EMI^{\left[1\right]}$

• Traces on outer layers of PCBs cause EMI<sup>[1]</sup>

$\bullet$  Traces crossing splits in power planes cause  $\mathrm{EMI}^{\mathrm{[2]}}$

• Ferrite beads in the power leads of devices is an effective way to reduce EMI. This action can reduce EMI but at the expense of degrading the performance of the device. This should never be done.

• Recessing the Vdd plane in from the ground plane reduces EMI. This is the notorious 20H rule<sup>[3]</sup>

• Splitting ground planes eliminates EMI. This turns the PCB into a dipole antenna.

#### EMI: WHAT IT IS, WHERE IT COMES FROM AND HOW TO CONTROL IT continues

• Connecting logic ground to the "chassis" in multiple places eliminates EMI. This allows currents that should stay in the ground structure two choices of where to flow, the ground structure or the case work.

• The  $\lambda/20$  rule. This rule states that logic ground should be connected to "chassis" ground at intervals of  $\lambda/20$ . Two assumptions have been made here. First, there is some frequency whose wavelength is  $\lambda/20$  that is more important than the rest. Second, that this thing called "chassis" ground is somehow EMI-neutral. Both of these assumptions are flawed. Following this rule is a good way to create an EMI problem by turning the chassis into an antenna.

• Connecting bypass capacitors directly to the power pins of ICs reduces EMI.

• Plating the sides of a PCB is necessary to contain EMI. Just review how close energy stays to the trace it travels on and it can be seen that this energy won't "stray" out to the edge of the PCB.

• Rows of ground vias are needed around the edges of a PCB to contain EMI. See above.

• Place a strip of metal all around the edge of a PCB on both sides connected to ground to contain EMI.

• Flooding outer layers of a PCB with ground does not reduce EMI.

• Connecting logic ground to "chassis ground" with capacitors at the mounting screws does not affect EMI.

#### **Can EMI Modeling Tools Predict EMI?**

There is a desire to find some modeling tool that can look at a potential design and predict where EMI may come from in order to allow changes to be made that will guarantee successful emissions testing. This is a noble goal. Unfortunately, it is well beyond the reach of any tools that are available on the market or are likely to be made available in the foreseeable future. If one looks at the complexity of the problem, it becomes clear why this is true. Implied in this goal is the ability to build a 3D model of the functioning product and then analyze it as it performs through the frequency band from 30 MHz to 1 GHz in three dimensions. This is a colossal task!

#### If Modeling Doesn't Work, What Does?

I have found that focusing on making very good power subsystems and making a good environment for transmission lines is the best practice. This minimizes the sources and the antennas. If the product has two PCBs joined by a connector or cable, it will need to be in a Faraday cage. Managing the antennas that leave the Faraday cage is an integral part of this task. **PCBDESIGN**

#### References

1. Brooks, Douglas. "90 Degree Corners, The Final Turn," *Printed Circuit Design*. January 1998.

2. Ritchey, Lee, "Test Lab, Cuts in Power Planes and Soldermask Effects on Impedance," *Printed Circuit Design*, January 2000.

3. Fang, Jiayuan, etal, "Effects of 20-H Rule and Shielding Vias on Electromagnetic Radiation From Printed Circuit Boards," UC Santa Cruz, Publishing date unknown.

4. Ritchey, Lee W. "Third in a Continuing Series of Test Lab Reports," *Printed Circuit Design*, April 2000.

5. Hubing, Todd H. et al, "Power Bus Decoupling on Multilayer Printed Circuit Boards," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 37, NO 2, May 1995.

6. Paul, Clayton R. "Introduction to Electromagnetic Compatibility," Wiley Inter-science, 1992. EMI Paper for Newsletter, Speeding Edge, March 2005

7. Ritchey, Lee W. and Zasio, John J. *Right the First Time: A Practical Handbook on High Speed PCB and System Design,* Speeding Edge, 2003.

Note: I have not listed the three books with the large number of errors and bad rules of thumb in them. Anyone wishing to obtain their names in order to avoid purchasing them can contact me through the web site, www.speedingedge.com.

Lee Ritchey is founder and president of Speeding Edge. A longtime PCB design instructor and consultant, Ritchey is the author of <u>Right the First Time:</u> <u>A Practical Handbook of High-</u> <u>Speed PCB and System Design</u>.

# PCB MANUFACTURING SUCCESS!

# We Have a Better Way to Predict

DFMStream provides powerful DFM capabilities in an easy-to-use tool suite designed to help engineers and designers verify design and manufacturing rules on PCB design databases, Gerber and NC data any time during the PCB design cycle. DFMStream bridges the gap between engineering and fabrication, helps save valuable time and reduces new product introduction bottle necks.

- Provides powerful DFM functionality

- Easy to learn, even for infrequent users

- Easy to implement as part of the everyday design flow

- Saves time and increases productivity

For more information visit downstreamtech.com or call 800-535-3226

#### Netlist errors are quickly validated in DFMStream

Define DFM checks by area so components such as BGAs can be verified with unique rules different from rest of design

# **A Small Leak Can Sink a Great Ship:** EMC Behavior of Traces Crossing Split Planes, Part I

#### Ralf Bruening ZUKEN

SUMMARY: Laying out a trace across a split or gap with reference planes is a major EMC design rule violation. But often, PCB designers have no alternative other than to place some signals that cross cutouts, gaps or voids underneath or above the routing path.

It has been known for several years, discussed regularly in all the relevant high-speed design books and found in practically all PCB design guidelines – a trace crossing a split or gap with reference planes is a major EMC design rule violation. Ignore this and you could significantly impact the return current and the noise behavior of the PCB.

Many of today's electronics contain large

ICs, such as FPGAs, ASICs or off-the-shelf processors that use multiple voltage rails. To maintain control over manufacturing costs, few electronic designers can afford to use the space for a full reference layer to support all the required voltage rails, including the reference planes to support the needed return path. Often, designers have no alternative other than to place some signals that cross cutouts, gaps or voids underneath or above the routing path.

But what might be considered a small design rule violation can impact the signal integrity behavior of single-ended and differential signals, as well as the overall EMC fingerprints of the PCBs. Violations like this increase the chance that the entire system will fail EMC testing.

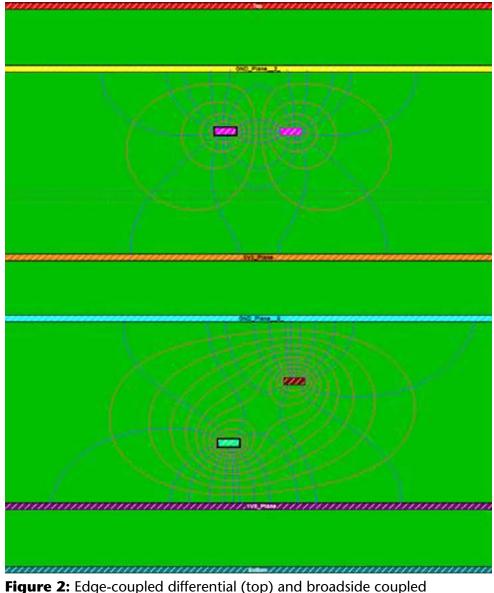

When reviewing possible violations, it's important to understand the difference between the behaviors of single-ended lines and coupled

# Quality PCBs from the established industry leader

With 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits<sup>®</sup> is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

## Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

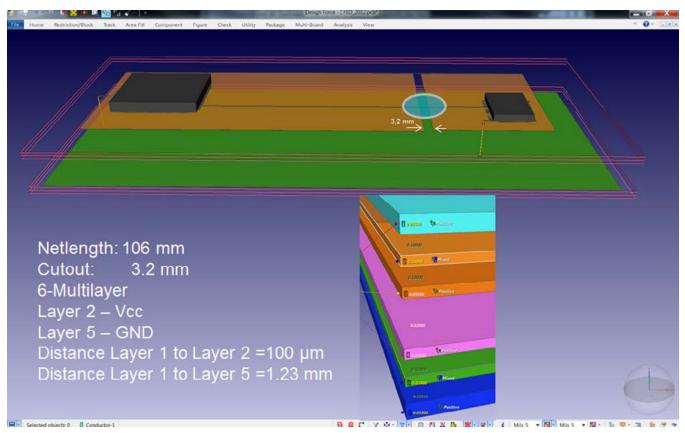

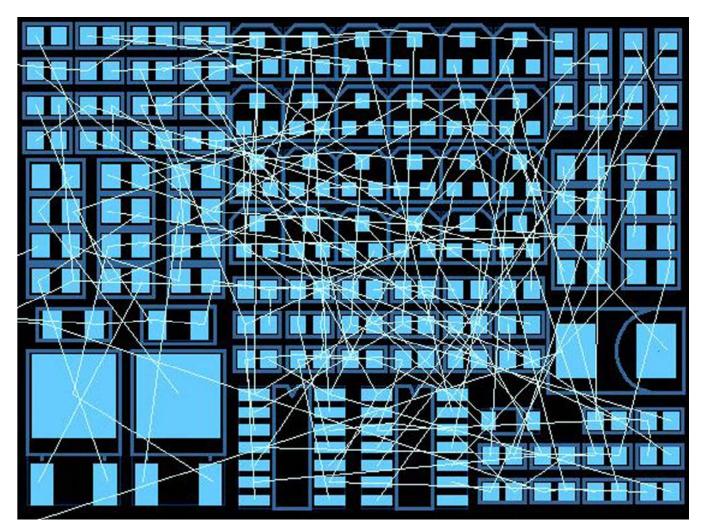

Figure 1: Signal crossing a split plane and board stack-up details in 3D within CR-8000 Design Force.

differential lines (which are commonly mistaken as immune to "bad" routing). Also, we need to study each case and the resulting impact on the design-related signal quality and EMC in terms of reflection, crosstalk levels, and the frequency domain behavior for resulting EMC farfield effects.

So let's start by doing a forensic study of a single trace crossing a split plane like the one shown in Figure 1.

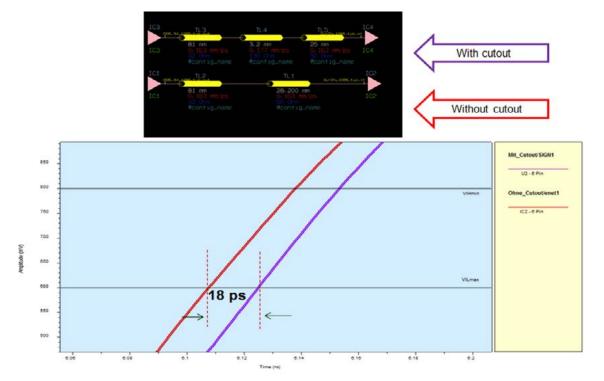

In this case we have a single-ended track on a small test design crossing a gap over a small distance of 3.2 mm. This can be easily extracted into an SI model to compare one signal with that small gap-crossing segment and the other signal without it. From there, the engineer can analyze the effect on the signal.

As you might expect, the quality of the signal that crosses the gap is affected. The ringing increases by 200 mV, which is significant for a 1.8V DDR3 output driver.

Signal quality is only one small piece of the

overall puzzle; since the signal switching for the logic levels is still within specification, you may assume that the impact is minimal and may be ignored. This may be true, but if we look more closely at the receiver switching, we will detect that there is a significant skew difference introduced by the small area crossing the gap, resulting in a skew difference up to 18ps on the receiver device.

When measuring signal timing with respect to voltage, a common rule of thumb is to allow 10% of the rise time as a margin. This example includes a fast DDR3 buffer (a Freescale DDR3 driver and Micron memory modules modeled by IBIS models). Following the 10% rule and considering that we have a buffer switching in the range of 270ps rise/fall time, this small routing mistake uses up a serious amount of the overall timing margin to cross the gap.

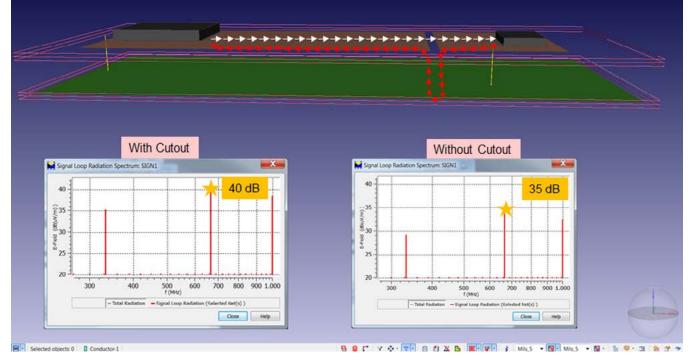

Now that we have looked at the signal integrity aspect of this for single-ended trace, let's look at the EMC footprint that results from this

IC2-1 (Pin): Extrema: Maximum: V = 1.770 V at t = 6.110 ns Minimum: V = -0.294 V at t = 21.084 ns IC4-1 (Pin): Extrema: Maximum: V = 1.918 V at t = 16.284 ns Minimum: V = -0.425 V at t = 11.277 ns

#### Difference: 148 mV

**Figure 2:** Comparison of voltage difference at the receiver for a signal with and without a cutout in the reference plane.

routing pattern. We know that the overall signal return path will increase due to the routing area crossing the gap. This will create quite an effective differential mode antenna where we can either use full-wave 3D solvers to precisely compute the electrical and magnetic field quantities, or we can use a max-emission calculator to quickly quantify the effects. (The calculator was developed by the EMC-Expert System Consortium at Missouri University of Science and Technology, formerly University of Missouri-Rolla.) The max-emission method is effective in capturing the efficiency of such PCB structure antennas, and is computed very quickly for any kind of routing patterns. The equation in Figure 4 is used to calculate the field strength of these antennas.

When applying this type of worst-case EMC emission analysis to a PCB structure with and without the signal pattern crossing the gap, you can expect the results illustrated in Figure 5.

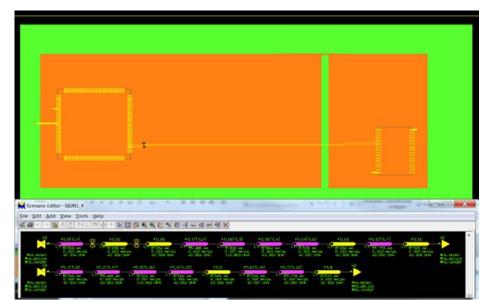

So far we have looked at an individual signal

line. On our example boards there are no single traces, but rather coupled signals that interfere with one another creating capacitive and inductive crosstalk effects. Now we need to determine if the trace crossing the split plane also impacts the crosstalk behavior.

Take the following configuration as an example: We have two lengthy coupled traces crossing a split. With such a large coupled area we can expect a significant amount of crosstalk.

Let's take a new test case where only a small

$$E(f)_{V/m} \leq \frac{Z_0 \pi I(f)A}{\lambda^2 R} = 1,316 \cdot 10^{-14} I(f)A f^2 \frac{1}{R}$$

R = The distance to the Antenna

A = Antenna size/area

I = frequency

**Figure 4:** Equation to estimate electrical field strength for differential-mode EMC emission.

#### Figure 3: Difference in signal delay at the receiver.

Figure 5: Estimated worst-case EMC emissions with and without reference plane cutout.

portion of the trace crosses the gap, we would expect to see less impact on the crosstalk voltages compared to a configuration that does not cross that gap. In both examples, a signal integrity simulator can help speed the design process by quickly computing voltage vs. time (note that coupled segments are shown in purple in the scratchpad editor, which depicts the extracted equivalent circuit model).

The result is rather surprising – we see in Figure 7 a significant increase in induced crosstalk with the traces crossing the cutout.

When comparing examples, the peak voltage of the example where the gap is crossed is nearly double that of the example without the gap.

So while it may seem minor, even a small design error on a single-ended trace can have significant impact on signal quality, timing, and EMC behavior. The result in our example shows a significant timing difference, double the amount of crosstalk voltage and a worst-case differential EMI of 5dbmV/m over frequency. How big are the margins in your designs? Designers should be aware of the possible pitfalls and decide on a

**Figure 6:** Schematic view derived from layout including coupled lines and equivalent circuit models for SI simulation.

**Figure 7:** Comparison of driver and receiver crosstalk voltages, with and without the signal crossing the cutout.

case-by-case basis if the design stands up to the risks, or if they will "sink" the printed circuit board ship. **PCBDESIGN**

This article is the first in a two-part series by Ralf Bruening.

Ralf Bruening is a product manager specializing in high-speed design, specifically signal and power integrity. He is based in Paderborn, Germany, at Zuken's EMC Technology Center.

#### CONNECTING THE DOTS

# **The Advantages of CAD**

#### by Jack Olson, CID+

SUMMARY: At this point in the story, the schematic has been packaged into the two types of data needed to start a circuit board layout: a part list and a net list. This month, Jack Olson offers a few final words about schematics and packaging and moves on to CAD libraries and PCB layout.

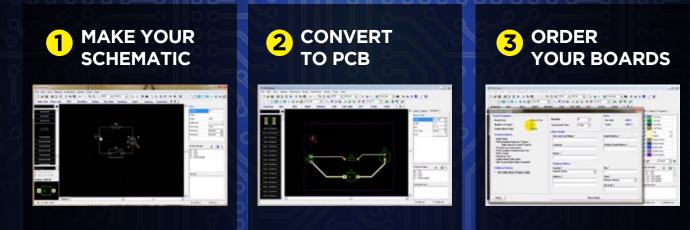

#### **Schematic Capture**

A schematic drawn on paper can be manually converted to a net list and part list to start a PCB layout, but from now on we'll turn our attention to circuit board design using computers. Most technical activities these days take advantage of the increased speed and accuracy of computer-aided design (CAD), so we'll leave the old methods for the historians to study. Software packages have been developed for electronics, and schematic concepts can be captured using a graphical user interface to do the following:

- 1. Select symbols from a CAD library

- 2. Place symbols on the screen

- 3. Connect the symbols together

You may not even need to assign reference designators or pin numbers to the symbols, unless you want to force specific arrangements (like connector pin assignments or logic gate assignments, for example) because the software can make these assignments automatically during the packaging process. The computer will or should make sure that each symbol is given a unique reference designator, assign pin numbers based on the selected component type, and report any conflicts or discrepancies. After the packaging process has been completed successfully, the schematic should be "backannotated" with the pin number and reference designator assignments. Modern technology can provide assistance in other ways, too. For example, circuits can be moved, rotated or copied into many similar circuits with just a few mouse clicks.

Most CAD software packages also support the placement of standard drawing borders, title blocks and notes. If you can customize the title blocks and notes to meet the needs of your

A SUBSIDIARY OF SHAX ENGINEERING

408.946.3446 sales@cbrcircuitsinc.com

# MANY TALK ABOUT QUALITY. WE GUARANTEE IT.

SCTION GUARAN

# SATISFACTION GUARANTEED

**E** 100%

We proudly stand behind every order with a 100% money back guarantee!

VIEW OUR GUARANTEE

CLICK TO VIEW

www.cbrcircuitsinc.com

#### THE ADVANTAGES OF CAD continues

customer or the company you work for, you can save a lot of time when starting a new design. Sometimes these edited features can be saved as templates, allowing the library to store several variations for different customers or applications.

#### **Net Properties**

Take advantage of any support your software provides for assigning net properties, net classes or component grouping. If you can define circuits with unique group names in the schematic, it may make it easier to organize the design in PCB layout, by making it easier to collect related parts together for component placement. It might even provide a method of maintaining clearances or other types of rules that can be applied to groups. In most designs you will be using a default trace width for routing connections between component pins, but you may need to use a wider trace width for higher current requirements. This can be managed by assigning properties to specific nets. You will probably set a default minimum clearance between conductive features, but there may be higher voltages in some areas that require a greater clearance. If you can assign net properties or define net classes in the schematic, the requirements will be much easier to manage in the PCB layout.

Voltage clearances and current requirements are the most common types of net properties and are used in even the simplest designs, but there could be other considerations that should be defined using net class or net property attributes, if possible. High-speed lines will need

Figure 1: A rat's nest.

#### THE ADVANTAGES OF CAD continues

to be impedance controlled using specific conductor width settings. Noise-sensitive circuits or safety specifications could drive larger clearance requirements in some areas. Signal timing issues may drive trace length

adjustments. Your design may eventually contain hundreds of different interrelated rules. Trying to manually check every rule in a complex design would be tedious and errorprone, so having the ability to embed them into the design, and having design rule check (DRC) software that can check them automatically can be real advantages. We may be good at pattern recognition and problem-solving, but computers are especially good at rule-checking. So to summarize, use the features provided by your software!

#### The Packaged Design

Now that we have a packaged PCB design database synchronized to a backannotated schematic, we can begin the layout. Your software may provide a list of components

to start placing, or it may just dump them randomly onto your screen for you to sort out. You might see all of the connections as lines from pin to pin; we call the view in Figure 1 a "rat's nest." You will eventually have to replace all of these lines with routed traces, adhering to the rules set for each net type.

I've mentioned before that the net list and part list are required to start a layout, but at this point the net connectivity will be maintained internally by the computer, and the physical part information will be drawn from a CAD library of "footprints" or "land patterns," so you won't strictly need them. You may want to export them as reports or as simple text files because they can be useful. Other people may need the part information for purchasing, as we've mentioned before. Send this information out as early as you can.

Trying to manually check every rule in a complex design would be tedious and error-prone, so having the ability to embed them into the design, and having design rule check (DRC) software that can check them automatically can be real advantages. We may be good at pattern recognition and problem-solving, but computers are especially good at rule-checking.

You should probably look through the net list at least once to check your net names. This can be important for designs that were packaged from large multi-sheet schematics, because

it's easy to make a mistake from one sheet to another. If you named

a net "+5V" on one sheet, and another sheet is labeled with "5V", they won't be connected in the layout. It will help if the list is alphabetized, so a discrepancy like two nets named "CLOCK" and "CLK" will be near each other, and you will notice them immediately. You may also see singlepin nets, which are nets that don't really go anywhere. Maybe you intended to connect the net on a different sheet and simply forgot about it, or used a different net name accidentally, but make sure to resolve any single-pin nets.

Finally, some CAD systems can report a list of spare gates. You will probably want to place spare gate symbols somewhere on your schematic (often on the last page) so you can

tie unused inputs high or low. It will also be useful information for human readers later on if they need to use a spare gate for something.

If you make any final changes, make sure you repackage the schematic again to keep it "in sync" with the layout, or use the ECO capabilities of your software to keep track of them automatically. **PCBDESIGN**

Jack Olson, C.I.D.+, has been designing circuit boards fulltime for over 20 years. He would like to thank Mark Marano and Les Asato for their companionship, and for leading him to his career

as a circuit board designer at Laser Precision Analytical. <u>Contact Jack here</u>.

# Most-Read PCB007 News Highlights

### Viasystems Q4 Results Hit by

**Fire in China Facility**

CEO David M. Sindelar says, "I expect first quarter consolidated net sales to be similar to our fourth quarter result, as we will experience the seasonal declines associated with the Chinese new year holiday and will be in the process of ramping production in our Guangzhou facility now that it has resumed full operations during the first quarter."

#### **IPC: PCB Shipments Down** 1.1% in January

"The book-to-bill ratio for the North American PCB industry strengthened for the second consecutive month, turning the corner in December after an eight-month downturn," according to Sharon Starr, IPC director of market research. "Sales and orders, however, remained sluggish in January."

#### CODI (Advanced Circuits) Posts \$5.2 Million Q4 Loss

Alan Offenberg, CEO of Compass Group Diversified Holdings LLC, stated, "We are pleased to post strong operating results for the fourth quarter and full year 2012. CODI's cash flow for the three and 12 months ended December 31, 2012 increased YoY by 38.6% and 12.6%, respectively."

#### IPC's PCB Market Report Predicts

#### **Growth for N.A. Market**

The North American PCB Market Report, published this week by IPC, predicts a modest return to growth in the North American PCB market in 2013. It also contains market data and a 2013 monthly sales forecast for rigid PCBs and flexible circuits.

#### TTM Restructures Equity Interest in DMC, SYE Plants

PCB manufacturer TTM Technologies Inc. has signed definitive agreements with its minority partner, Shengyi Technology Co. Ltd. (Sytech), to sell TTM's 70.2% equity interest in the SYE plant to Sytech and to acquire Sytech's 20% equity interest in the DMC plant.

#### **Graphic Embeds RFID into PCBs**

Graphic PLC presented a controversial paper at the EIPC Berlin Conference sharing information regarding its development project on embedding radio frequency identification (RFID) in collaboration with the University of Exeter.

#### Global PCB Industry's Growth Rate to Slow in 2013

In 2012, the global PCB industry saw a jump in terms of output value, benefiting from a rapid growth in shipments from Apple and Samsung, to 7% over 2011 levels to US \$62B. The report sees no such possibility for such a large jump in 2013 and expects that the growth rate will slow to 2.7%.

#### Aspocomp Disappointed with 2012 Results

"2012 started reasonably well, but ended in disappointment. In spite of the acquisition of the Teuva plant, our net sales remained on par with the previous year. The second plant increased our indirect costs, depressing profit to EUR 0.6M, or 3% of net sales. Cash flow from operations was clearly in the black, around EUR 1.2 million," said Sami Holopainen, CEO.

#### **IPC Conference to Focus**

#### on Big Picture

The need to look at the big picture or the whole electronic system rather than focusing on its individual parts is the impetus of the IPC Electronic System Technologies Conference and Exhibition (ESTC).

#### **EIPC Endorses The PCB List**

The EIPC writes in its endorsement, "The PCB List was created by I-Connect007/PCB007 as a tool for buyers and specifiers to quickly and easily find PCB manufacturers, anywhere in the world. We have reviewed The PCB List and it is indeed as stated, 'the world's most comprehensive online directory of PCB manufacturers, anywhere.'"

# Delivering the highest quality standard for Aerospace and Defense

### Ventec Accredited to AS9100 Rev. C

We are proud to announce that our parent company, Ventec Electronics Suzhou Co Ltd, is now fully certified to AS9100 Revision C.for both the design and manfacture of copper clad laminate and prepreg for aerospace applications.

AS9100 is the quality management standard specifically written for the aerospace and defence industry, to satisfy authorities such as the Federal Aviation Administration, ensuring quality and safety in the "high risk" aerospace industry.

### MORE INFO: POLYIMIDE & HIGH RELIABILITY FR4 PRODUCTS Wherever technology takes you, we deliver. Vertice Accredited AS9100 Rev C

Ventec Europe www.ventec-europe.com Ventec USA www.ventec-usa.com Ventec International Group www.venteclaminates.com

#### LIGHTNING SPEED LAMINATES

# Microwave Radiation Loss Concerns in PCBs

by John Coonrod ROGERS CORPORATION

SUMMARY: A general definition of radiation loss is the energy on the circuit that is lost by radiating away from the circuit and into the surrounding environment. The lost energy has to go somewhere, and this can be a source of EMI issues. These losses become more prevalent at high frequencies, and designers must be aware of potential interactions between design techniques and circuit materials.

Circuits used at high frequencies, such as microwave frequencies, are prone to radiation losses. There are typically circuit design dependencies, but the circuit material may have an effect as well, and designers should be aware of potential interactions between the design techniques and circuit materials.

A typical PCB used at microwave frequencies experiences total loss, or insertion loss, made up of four different loss components: conductor, dielectric, leakage, and radiation losses. RF leakage losses at microwave frequencies are generally not an issue when using PCB materials; however, conductor losses and dielectric losses are definitely an issue. Radiation losses depend on the circuit configuration, design, material thickness, dielectric constant and frequency. A general definition of radiation loss is the energy on the circuit that is lost by radiating away from the circuit and into the surrounding environment. The lost energy has to go somewhere, and this can be a source of EMI issues.

Impedance mismatches can be a significant source of radiation loss. Normally the designer will try to match impedances, but some scenarios in microwave design require different impedance levels. Another issue, which is sometimes related to impedance mismatch, is radiation loss due to signal launch. Signal launch happens where the connector meets the circuit board. In this area, the signal energy has to transition from the coaxial wave propagation mode of the connector to the planar mode of the PCB. The signal launch areas can have significant radiation loss and the microwave designer will typically put a lot of effort into trying to quiet that transition.

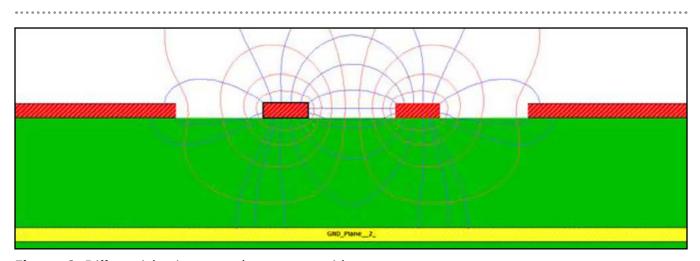

Circuit losses due to radiation are generally not an issue with stripline configurations, and can be much less of a concern with grounded coplanar constructions. The single-ended microstrip transmission line is more prone to radiation loss and there are several issues which

| MICROWAVE RADIATION LOSS CONCERNS I | N PCBS | continues |

|-------------------------------------|--------|-----------|

|-------------------------------------|--------|-----------|

| 0 ohm microstrip, Dk=3.66, Df=0.0037, thickness=6.6mil |              |              |              | 50 ohm microstrip, Dk=3.66, Df=0.0037, thickness=20mil |       |              |              |              |              |

|--------------------------------------------------------|--------------|--------------|--------------|--------------------------------------------------------|-------|--------------|--------------|--------------|--------------|

| Freq                                                   | Dielectric   | Conductor    | Radiation    | Total                                                  | Freq  | Dielectric   | Conductor    | Radiation    | Total        |

| (GHz)                                                  | Loss (dB/in) | Loss (dB/in) | Loss (dB/in) | Loss (dB/in)                                           | (GHz) | Loss (dB/in) | Loss (dB/in) | Loss (dB/in) | Loss (dB/in) |

| 1                                                      | -0.012       | -0.114       | 0.000        | -0.127                                                 | 1     | -0.012       | -0.037       | 0.000        | -0.051       |

| \$                                                     | -0.063       | -0.284       | -0.001       | -0.349                                                 | 5     | -0.064       | -0.094       | -0.011       | -0.170       |

| 10                                                     | -0.127       | -0.408       | -0.005       | -0.540                                                 | 10    | -0.130       | -0.136       | -0.046       | -0.313       |

| 15                                                     | -0.191       | -0.503       | -0.011       | -0.705                                                 | 15    | -0.198       | -0.168       | -0.103       | -0.470       |

| 20                                                     | -0.255       | -0.583       | -0.020       | -0.859                                                 | 20    | -0.268       | -0.196       | -0.183       | -0.647       |

| 25                                                     | -0.321       | -0.654       | -0.031       | -1.007                                                 | 25    | -0.339       | -0.221       | -0.284       | -0.845       |

| 30                                                     | -0.386       | -0.718       | -0.045       | -1.151                                                 | 30    | -0.413       | -0.244       | -0.407       | -1.064       |

**Figure 1:** Comparison of losses for microstrip transmisison line circuits, of different thickness while using the same substrate material.

can vary the amount of loss. As general statements, a thicker circuit will have more radiation loss than a thinner circuit. A circuit with a low dielectric constant will have more radiation loss than a circuit with high dielectric constant. Applications operating at lower frequencies will have less radiation as compared to those at higher frequencies. Finally, there are interactions between all of these conditions, which can complicate the understanding of radiation loss in circuit designs.

To demonstrate some different scenarios, several examples will be given regarding radiation loss. The software modeling tool that will be utilized is MWI-2010, which is free to <u>down-load here</u>. This software can predict insertion loss of a microstrip circuit and show the different components of this loss.

The first example shows differences in radiation loss when using the same substrate, but at different thicknesses. Figure 1 illustrates a comparison in losses of two 50 ohm microstrip transmission line circuits built on the same high-frequency laminate. The first circuit is using a laminate of 6.6 mils thickness, and the second circuit's laminate is 20 mils thick. The laminate has a dielectric constant of 3.66, dissipation factor of 0.0037 and is commonly used in high-frequency applications.

It can be seen in Figure 1 that the table on the left for the thinner circuit has much lower radiation losses than the table on the right for the thicker circuit. It is also obvious that the radiation losses are frequency dependent and the higher frequencies have the higher radiation loss values.

The next example demonstrates the differences in radiation losses for circuits using the same thickness of matieral, but with different dielectric constants. Figure 2 shows a comparison of 50 ohm microstrip transmission lines using high-frequency laminates of 20 mil thickness, with a dielectric constant of 2.20 and 4.50.

| 50 ohm m      | nicrostrip, Dk=            | 2.20, Df=0.00             | 09, thickness             | =20mil                | 50 ohm m      | nicrostrip, Dk=            | 4.50, Df=0.00             | 2, thickness=             | 20mil                 |

|---------------|----------------------------|---------------------------|---------------------------|-----------------------|---------------|----------------------------|---------------------------|---------------------------|-----------------------|

| Freq<br>(GHz) | Dielectric<br>Loss (dB/in) | Conductor<br>Loss (dB/in) | Radiation<br>Loss (dB/in) | Total<br>Loss (dB/in) | Freq<br>(GHz) | Dielectric<br>Loss (dB/in) | Conductor<br>Loss (dB/in) | Radiation<br>Loss (dB/in) | Total<br>Loss (dB/in) |

| 1             | -0.002                     | -0.016                    | 0.000                     | -0.019                | 1             | -0.007                     | -0.036                    | 0.000                     | -0.045                |

| 5             | -0.012                     | -0.039                    | -0.014                    | -0.066                | 5             | -0.038                     | -0.103                    | -0.010                    | -0.152                |

| 10            | -0.024                     | -0.060                    | -0.056                    | -0.142                | 10            | -0.078                     | -0.151                    | -0.042                    | -0.272                |

| 15            | -0.037                     | -0.079                    | -0.127                    | -0.244                | 15            | -0.118                     | -0.189                    | -0.095                    | -0.403                |

| 20            | -0.050                     | -0.097                    | -0.225                    | -0.373                | 20            | -0.160                     | -0.221                    | -0.168                    | -0.550                |

| 25            | -0.063                     | -0.115                    | -0.350                    | -0.529                | 25            | -0.203                     | -0.250                    | -0.261                    | -0.714                |

| 30            | -0.077                     | -0.131                    | -0.502                    | -0.711                | 30            | -0.247                     | -0.276                    | -0.373                    | -0.897                |

**Figure 2:** Comparison of losses for microstrip transmisison line circuits, with different dielectric constant, using the same substrate thickness.

#### lightning speed laminates

#### **MICROWAVE RADIATION LOSS CONCERNS IN PCBS** continues

Figure 2 illustrates how a microstrip circuit with the same laminate thickness will have different radiation losses when using substrates with a different dielectric constant. The table on the left has much more radiation loss when using material with a dielectric constant of 2.20 than the table on the right with a circuit that features material with a dielectric constant of 4.50.

It can also be seen in Figure 2 that the dissipation factor (Df) is very different between these two materials. The Df mainly affects dielectric losses. The conductor losses are mostly dominated by copper properties, conductor width and surface roughness. Even though the material with a higher dielectric constant will have less radiation loss, it is necessary to have a narrower conductor width to maintain a 50 ohm trace, so the conductor losses will be higher than a circuit with a lower diectric constant. This is one of many tradeoffs that are to be expected when considering the proper material for an application. Radiation loss can be problematic for microwave PCB performance, however, it can also cause issues by radiating energy to neighboring conductors and components on the PCB. A thorough understanding of radiation loss can help to minizize EMI issues as well as optimizing the circuit for higher-frequency performance. **PCBDESIGN**

John Coonrod is a market development engineer for Rogers Corporation, Advanced Circuit Materials Division. About half of his 25 years of professional experience has been spent in the flexible PCB

industry doing circuit design, applications, processing, and materials engineering. Coonrod has also supported the high-frequency, rigid PCB materials made by Rogers for the past 10 years. <u>Reach Coonrod here</u>.

### video Interview

## Lee Ritchey: Seeking the Limits of Materials

#### by Real Time with... PCBDesign007

At what speed will current materials fail? Lee Ritchey and Isola teamed up on this 16-layer test board that's designed to plumb the absolute limits of today's materials. Lee presented a well-attended paper on this subject at DesignCon 2013.

#### FTG's New Facility Now Certified to AS9100C

FTG Aerospace - Chatsworth, a subsidiary of Firan Technology Group Corporation, has achieved certification to the ISO9001: 2008/AS9100 Revision C standard. FTG Aerospace - Chatsworth is the fifth FTG manufacturing facility to achieve AS9100 Revision C certification, demonstrating FTG's commitment to investing in its quality management systems.

#### Circuit-Tech Inc. Earns AS 9100C Certification

This AS9100C certification reflects the company's commitment to continuous improvements. Circuit-Tech Inc. also holds certificates for MIL-PRF 55110, ISO 9001-2000, and ISO 9001-2008, as well as the Canadian Controlled Goods Certificate.

#### Invotec Wins SC21 Bronze Award

Invotec Group's Tamworth facility has received the SC21 Bronze Award. To net this recognition, Invotec achieved delivery and quality performance standards for all of its key customers over a rolling 12-month period.

#### Lab Circuits Earns UNE-EN 9100:2010

Lab Circuits has been awarded the UNE-EN 9100:2010 certification for its Quality Management System, as required in the aviation, space, and defence sectors. In November, Lab Circuits successfully passed the certification audit for the quality standard UNE-EN 9100:2010 by AENOR.

#### <u>China, India, Brazil Key Markets for</u> <u>Defense Growth</u>

According to the survey results, 78%, 73%, and 56% of respondents from defense organizations identified 'cyber warfare,' 'UAVs,' and 'soldier modernization' as the most important defense segments that will show the most technological advancement over the next decade.

#### U.S. Defense Market Driven by Modernization

Research and Markets has announced the addition of the "Future of the U.S. Defense Industry - Market Attractiveness, Competitive Landscape and Forecasts to 2017" report to their offerings.

#### **Technology Integration Vital to Ensure Enhanced Security**

Constant threats related to terrorism and natural disasters are pushing city officials to build secure environments for residents. In order to ensure enhanced security that does not strain city budgets, optimization and integration of security technologies is imperative.

#### Global Military Comm & COTS Market at \$17.46B in 2013

The Global Military Communications & COTS Market 2013-2023, Visiongain's latest defense and security report, values the market for military communications spending to reach \$17.4B in 2013, as both mature and emerging national markets invest in advanced military communications networks.

#### Defense Industry to See Significant M&A Trend in 2013

The global defense industry witnessed significant M&A activity in 2012. The prevalent unstable economic environment and consequent federal military budget cuts in the major spending countries of North America and Europe resulted in consolidation as a primary growth strategy for companies.

#### Report Reveals Continued Decrease in Defense Sector Revenue & Earnings

Defense firms revenue decreased 1.5% and earnings fell 7.4%, while commercial aerospace revenue increased 18.3% and earnings increased by 13%.

#### **DESIGN FOR MANUFACTURING**

# The Ten Commandments of Design for Assembly

#### by Amit Bahl

SUMMARY: The best way for designers to avoid problems during assembly is to communicate thoroughly and frequently with your assembly provider. But, just in case, columnist Amit Bahl has created the Ten Commandments of DFA.

You might think that most PCB designers would know how to avoid the most obvious blunders that can gum up board assembly. But you would be wrong. I can tell you from daily experience that we're just not there yet. So allow me to propose the Ten Commandments of DFA.

#### **1st Commandment**

Be sure all indicators are present. The leading show-stopper in assembly is missing pin 1 indicators or comAlternatively, use the electrical symbol for diodes in the correct orientation to guide assembly. Never indicate diode polarity based on the anode pad. Use a K to designate the cathode or line up the diode symbol in the correct position. Don't substitute any other marks or your contractor will misinterpret what you intend.

To orient tantalum capacitors, tag the positive side with a plus symbol on the silkscreen. Remember, tantalum capacitors can ignite if mounted with swapped polarity. Short of reverse-engineering a schematic (and who bundles schematics with assembly files?) there's no way for a contractor to figure out part polarity unless it's clearly displayed.

Silkscreens must not interfere with pads, and symbols should not be printed beneath the body of any component.

#### 2<sup>nd</sup> Commandment

Vias in pads must be filled, unless they reside in thermal pads. The pad matrix on which a BGA will be installed may include through vias and blind vias, but all of them must be filled and

> planarized, or solder joints will be compromised.

In corporate vias in the thermal pads under QFNs to help solder flow through to conductive planes. The vias ensure a secure solder joint for the thermal pad and prevent solder from floating the

ponent polarity/orientation indicators on the silkscreen. Nearly 75% of the assembly orders my facility receives fail to identify the location of pin 1 for each IC, or they misrepresent or neglect to indicate the polarity of some capacitors, diodes, or LEDs.

Obey the convention for marking the polarity of diodes, including LEDs: Put a K on the silkscreen layer at the cathode end.

# Halogen Free. Lead Free. Worry Free.

# MCL-HE-679G/Theta **Circuit Materials**

MCL-HE-679G/Theta materials are environmentally friendly halogen free high-speed digital materials, delivering excellent electrical performance and superior CAF resistance.

These materials demonstrate robust thermal performance through 260°C lead free assembly, offering uncompromised reliability for high layer counts with fine pitch BGAs and stacked microvia designs.

Compare the Advantages of MCL-HE-679G/Theta Materials

- Excellent electrical performance: Dk of 3.9 and dissipation factor of 0.009 at 1 GHz

- Thermally robust: Tg of +180°C and Td of +370°C

- Reliable: 30% less z-axis expansion with temperature than high-Tg FR-4

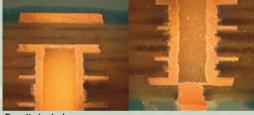

**Example Test Vehicle** 18 layer, .085" thick (2.16 mm), buried and single stack vias. 2 lamination cycles (1+N+1).

(Magnified @ 100x)

1010100000000

#### Results include:

- 10x reflow @ 260°C (JEDEC std. lead free cycle) ,

- 6x 260°C preconditioning before 1000 cycles IST @ 150°C followed by 100 cycles @ 190°C

- CTEz (50-260°C) of 3.1%

www.rogerscorp.com/theta

Advanced Circuit Materials Division The world runs better with Rogers.®

#### USA - AZ tel. +1-480-961-1382 EUROPE - BELGIUM tel. +32-9-235-3611 CHINA tel. 86-21-62175599

\*Hitachi Chemical Co., Ltd. and Rogers Corporation are collaborating on circuit board materials for use in high speed digital applications. "MCL" is a registered trademark of Hitachi Chemical Co., Ltd., in USA and other countries. "THETA" is a registered trademark of Rogers Corporation.

#### THE TEN COMMANDMENTS OF DESIGN FOR ASSEMBLY continues

package during assembly, which could hamper forming good solder joints at the QFN contacts. An assembly shop can compensate for a lack of through vias in a thermal pad by adding a windowpane-shaped opening in the solderpaste stencil above the pad, to relieve solder pooling and outgassing during assembly, but the fix is less effective than if vias were present.

## 3<sup>rd</sup> Commandment

Every connection to every component must have its own independent pad. Each pad must be commensurate in size with its mates.

If two components share a pad – let's say, a resistor and a capacitor – neither can be properly aligned during assembly. And if one pad is substantially larger than its mate for a component, component tombstoning can result from an imbalance of solder deposition.

If a pour or plane will be a point of contact, there must be a mask-defined pad of appropri-

ate size. If a device involves non-soldermaskdefined pads for connections as well as soldermask-defined pads – a BGA matrix on a loose pitch in which some adjacent outer balls are common to a ground pour, for example – stipulate in a design note that the board fabricator shall not edit the soldermask apertures for those soldermask-defined pads.

#### 4<sup>th</sup> Commandment

Never mix lead-free components with components that are not specified for leadfree assembly. If any component requires lead-free assembly and no substitute for conventional leaded solder is available, then the entire board must be assembled lead-free and all components must be qualified for lead-free assembly.

Sometimes the only package available for a particular device is a lead-free BGA. However, boards that will be used for military projects

**Figure 1:** A breakaway tab that remained between these boards after routing interfered with assembling a connector that extends over that edge. Such problems occur when board fabrication and assembly are not closely coordinated.

# THE TEN COMMANDMENTS OF DESIGN FOR ASSEMBLY continues

typically must be assembled with conventional leaded solder, per government requirements. The designer must either obtain a waiver from the customer to allow lead-free assembly; modify the design to use a device that is available in a package for assembly with conventional leaded solder; or have the BGA reballed for leaded solder (an expensive procedure that can damage parts).

### 5<sup>th</sup> Commandment

Adhere to spacing guidelines, including clearances at board edges. If connectors or other hardware will overlap a board edge, and the boards will be fabricated by one vendor and assembled by another, instruct the fabricator where the connectors will sit and to route panels such that no material remains that would interfere with the connectors during assembly (Figure 1).

## 6<sup>th</sup> Commandment

Distribute large components across a board as evenly as possible during layout, to achieve the best possible thermal distribution during solder reflow. Make sure the assembly contractor tailors a thermal profile for the reflow oven unique to each assembly job.

### 7<sup>th</sup> Commandment

Format every bill of materials according to Figure 2, to precisely identify all of the components to be assembled on each board. The properly formatted BOM has columns indicating:

- full manufacturer's part number

- manufacturer's name

- item number

- quantity per board

- reference designators, separated by commas

- a complete part description

It may also include:

- distributor's name

- distributor's part number

## 8<sup>th</sup> Commandment

Boards should be provided as arrays in panels for assembly if they are very small, especially those smaller than 3" x 3". All irregularly shaped boards (circular, oval, L-shaped, etc.) should be arrayed to facilitate handling. Some contractors can assemble a limited number of such small or odd-shaped boards individually, using universal fixtures.

Follow these guidelines:

• One BOM for the entire panel. For example, if there are four different boards called A, B, C, D, a single BOM must list all of the components for all four boards combined.

• None of the reference designators can be repeated from one board to another. For example, if R1 will be assembled on board A, it cannot be used as a designator on any of the other boards. If a part of the same value is required on other boards, it must be designated differently for each board.

| Part Number         | ltem | qty | Designator           | Description                         | Mank |

|---------------------|------|-----|----------------------|-------------------------------------|------|

| C2012X5R1C106K/1.25 | 1    | 1   | C1                   | CAP CER 10UF 16V 10% X5R 0805       | TDK  |

| C2012X5R0J476M      | 2    | 1   | C2                   | CAP CER 47UF 6.3V X5R 20% 0805      | TDK  |

| C1608X7R1A105K      | 3    | 5   | C3, C132, C133,      | CAP CERAMIC 1.0UF 10V 0.1 X7R 0603  | TDK  |

|                     |      |     | C136, C137           |                                     |      |

| C2012X5R1A226K/1.25 | 4    | 4   | C4, C16, C19, C24    | CAP CER 22UF 10V 10% X5R 0805       | TDK  |

| C1005X5R0J104K      | 5    | 15  | C5, C6, C7, C8, C9,  | CAP CERAMIC .10UF 6.3V 0.1 X5R 0402 | TDK  |

|                     |      |     | C10, C11, C12, C13,  |                                     |      |

|                     |      |     | C14, C15, C20, C118, |                                     |      |

|                     |      |     | C119, C120           |                                     |      |

Figure 2: Prepare the BOM for every project in exactly the same format. Adhere to this example.

#### design for manufacturing

#### THE TEN COMMANDMENTS OF DESIGN FOR ASSEMBLY continues

**Figure 3:** A proper kit would contain one contiguous tape of this component, including overage.

• Placement must be guided by a single set of XY data for the entire panel in correlation with the single, combined BOM.

#### 9<sup>th</sup> Commandment

Needless to say, it's far better to catch issues that might impede assembly before the boards are fabricated. If the board will be fabricated and assembled by the same facility (thereby coordinating operations), verify whether to provide the design data in ODB++ format to speed identifying potential manufacturing issues and ease CAM setup. Outputting a design in ODB++ captures the data for fabrication, assembly, and test in a unified structure that supports automated analysis and avoids time-consuming data conversion at the CAM stage. Practically all major EDA platforms can output design data in the ODB++ format.

# **10<sup>th</sup> Commandment**

Technically, the 10th commandment does not address design, but component delivery to the contractor. If assembly will be performed on a consignment basis – some or all of the components will be supplied by the assembly customer, instead of being procured by the assembler – the parts must be provided in a carefully organized kit matching the BOM. All SMT components must be supplied in reels, or on continuous tapes at least 6" in length, or in tubes or trays.

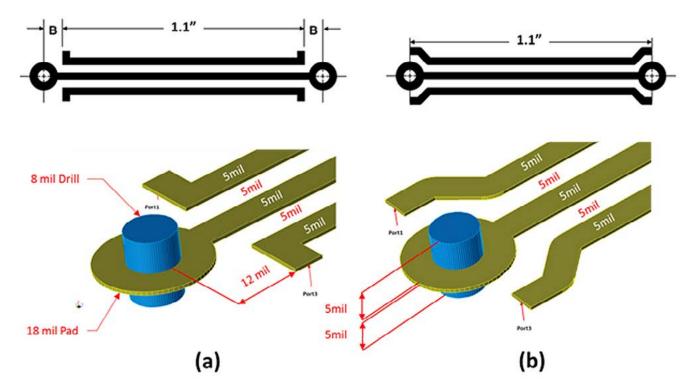

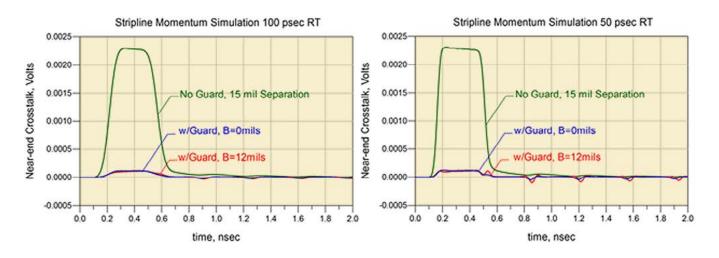

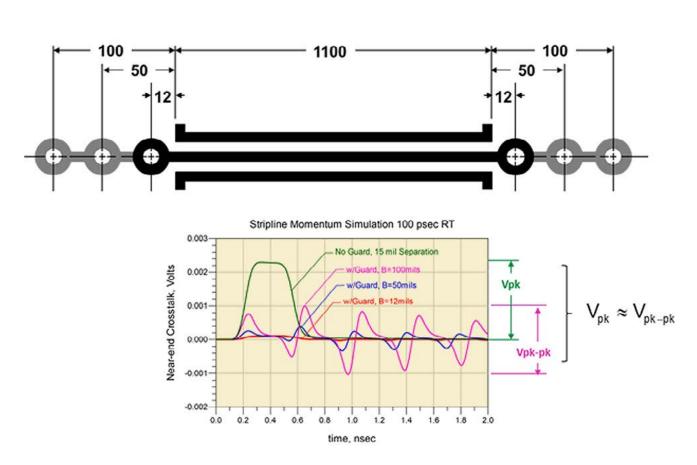

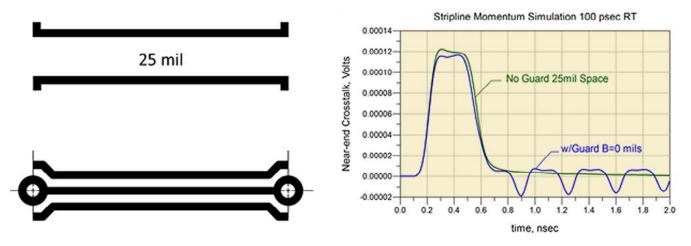

Extra components are required for every part number listed on the BOM, to cover attrition during assembly. For example, an assembly shop may require a minimum of 100, or 20% more 0201 1k ohm resistors than called for on the BOM. The parts for each line item on the BOM must be sent in a clearly marked bag separate from the other parts. All ICs must be shipped in their original, unopened protective packages that include desiccant, or else they must be baked for eight hours or so to remove moisture before assembly, which could set back assembly for a day.