Measuring Correlation to 50 GHz and Beyond p.10

Postmortem Simulation p.28

Efficient Simulation Using High-Frequency Printed Circuit Materials p.36

High-Speed Boards Need Automated Checking p.54

### **SIMULATION & ANALYSIS**

### THE best way to find a PCB fabricator, anywhere.

- Free access to the definitive directory of PCB fabricators

- The most comprehensive list from around the world

- In-depth profiles of PCB fabricators

- Easy to use, with intuitive navigation

- Quick searches to locate the right fabricator

- In-depth searches for specific capabilities

### The Next Generation High Speed Product from Isola

- Global constructions available in all regions

- Optimized constructions to improve lead free performance

- I-Speed delivers 15-20% lower insertion loss over competitive products through reduced copper roughness and dielectric loss

- Improved Z-axis CTE 2.70%

- I-Speed IPC 4101 Rev. C /21 /24 /121 /124 /129

- Offer spread and square weave glass styles (1035, 1067, 1078, 1086, 3313) for laminates and prepregs

- Minimizes micro-Dk effects of glass fabrics

- Enables the glass to absorb resin better and enhances CAF capabilities

- Improves yields at laser and mechanical drilling

- A low Df product with a low cost of ownership

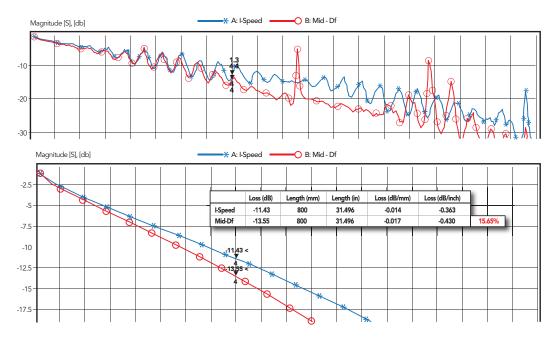

### Effective Loss @ 4 GHz on a 32 inch line

I-Speed delivers 15-20% lower insertion loss over competitive low Df products.

http://www.isola-group.com/products/i-speed

The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these materials will be governed by the terms and conditions of the agreement under which they are sold.

Isola Group S.a.r.l. 3100 West Ray Rd., Suite 301, Chandler, AZ 85226 1-480-893-6527 http://www.isola-group.com

### **FEATURED CONTENT**

Do you run simulation on your PCB designs? Circuit boards have grown increasingly faster and more complex, yet simulation is still not standard procedure, even with high-technology designs. This month, our veteran contributors discuss a variety of simulation techniques that can help you save time and avoid costly re-spins.

### 28 Postmortem Simulation by Barry Olney

### 54 High-Speed Boards Need Automated Checking

by Mike Steinberger

### FEATURE COLUMN

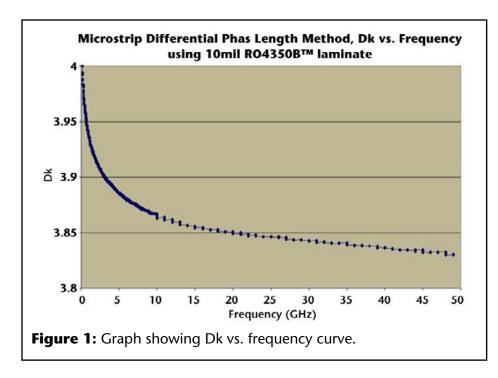

**36 Efficient Simulation Using High-Frequency Printed Circuit Materials** *by John Coonrod*

Storage

Military

Backplane

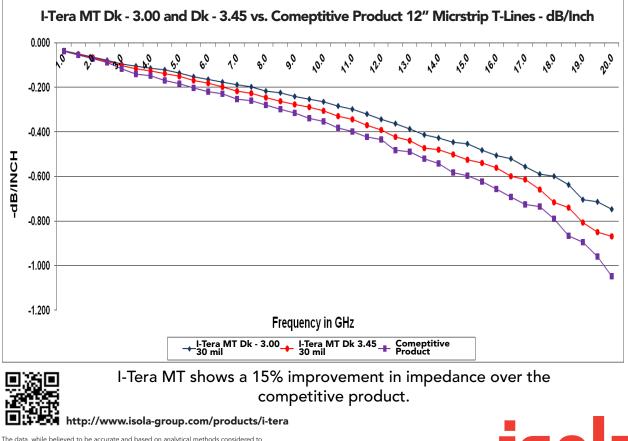

### Servers The Next Generation Very Low Loss Product from Isola

era

R

• Tg - 200°C

Infrastructure

Telecom

- Td 360°C

- Low CTE in the Z-axis 2.8% (50 to 260°C)

- Dk range = 3.00 to 3.45

- Df range 0.0030 to 0.0036

- Utilizes standard E-glass

- Exhibited good filling of vias vs. competitive products

- Global availability with standard constructions

- Square-weave styles available: 1035, 1067, 1078, 1086, 3313

- Superior processing performance over competitive products

- I-Tera MT processing attributes:

- 30% greater press productivity over competitive products

- Better drilling performance over competitive products, no ceramic filler used

- No plasma desmear required

- I-Tera MT prepreg standard FR-4 storage conditions apply

- UL Qualified 130 MOT

The data, while believed to be accurate and based on analytical methods considered to be reliable, is for information purposes only. Any sales of these materials will be governed by the terms and conditions of the agreement under which they are sold.

Isola Group S.a.r.l. 3100 West Ray Rd., Suite 301, Chandler, AZ 85226 1-480-893-6527 http://www.isola-group.com

### **150** The base for innovation

FEBRUARY 2013

VOLUME 2

NUMBER 2

thepcbdesignmagazine.com

THE OPTIMUM MAGAZINE DEDICATED TO

PCB DESIGN

### **CONTENTS**

AN CONNECTOR PUBLICATION

MAGAZINE

40 IPC APEX EXPO 2013 Pre-Show Coverage

### ARTICLE

70 Is the Cloud a New Paradigm for Electronic Design? by Dr. Raul Camposano and Steven McKinney

тн≣ЮСр

### **SHORTS**

- 9 IPC: December 2012 Shipments, Bookings Down

- 27 2013 Design Vision Award Winners Recognize Innovation

- 63 Nanowires Could Lead to More Efficient, Cheaper Solar Cells

- 80 IPC Sees Bright Future for Latin American Industry

### TOP TEN MOST-READ NEWS

- 35 PCB007

- 63 Mil/Aero007

COLUMNS

8 To Simulate or Not to Simulate? by Andy Shaughnessy

- 22 PCB Design Data: What Do Your Customers Expect? by Jack Olson

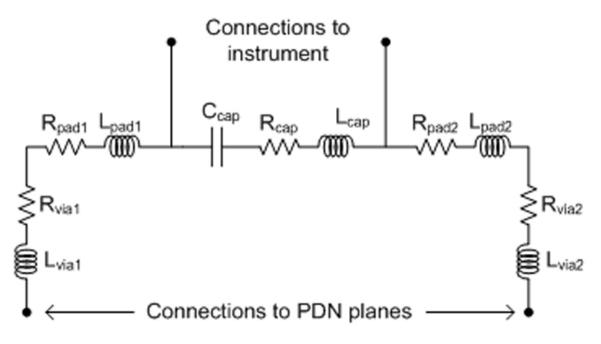

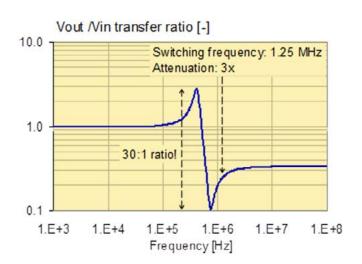

- 64 Do Not Measure PDN Noise Across Capacitors! by Istvan Novak

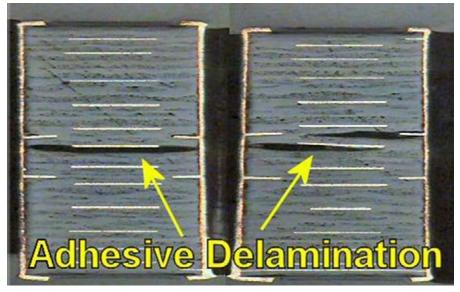

- 76 Adhesive Delamination by Paul Reid

### **VIDEO INTERVIEWS**

- 21 Simberian: High-End Simulation For Designers

- 27 Cadence Integrates Sigrity Capabilities

- 68 Modeling High-Speed Structures: The Doctor is In

- 74 Twenty-Five Years of Simulation Stimulation

- EXTRAS 84 Events Calendar

85 Advertiser Index & Masthead

## **BRINGING YOUR DESIGN**

## **TO FRUITION**

At U.S. Circuit we stand ready to serve PCB Designers as they are faced with the challenge of executing their brilliant ideas. Here are just a few of the services we offer to help get you on your way:

- Impedance Control Calculations & Detail Stack-Up Creation

- Design Services Through Local PCB Design Partners

- Film-to-Gerber Conversion

Contact us for a quote today!

U. S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 Ph: (760) 489-1413 Fax: (760) 489-2965

### Superior Quality Superior Service

www.uscircuit.com

ITAR Registered

ISO 9001:2008

MIL-PRF-55110G

### THE SHAUGHNESSY REPORT

### **To Simulate or Not to Simulate?**

#### by Andy Shaughnessy

I-CONNECT007

Years ago, very few PCB designs went through any type of simulation process. And that was just fine. Most designs were simple enough; they didn't need to be simulated.

But then high-speed design became the rule,

So Ansoft was acquired by ANSYS, HyperLynx and Zeland are now part of Mentor Graphics, and Sigrity was purchased by Cadence last year. Only Agilent, CST, E-System Design, Simberian and SiSoft remain independent. Agilent

rather than the exception. Now designers and design engineers are contending with issues such ever-increasas ing edge rates, transmission line reflections, ground bounce, and crosstalk, not to mention challenges related to DDR, PCi XAUI. Express, and SERDES.

Simulation software became a big segment of our industry. Over the past few decades, we've seen companies like Ansoft, Agilent, CST, E-

System Design, HyperLynx, Sigrity, Simberian, SiSoft, and Zeland develop PCB simulation and analysis solutions.

These companies used to exhibit at all of the industry trade shows, from DesignCon to MTT/S to PCB West. But over the years, many of them have been absorbed by the "big guys."

The EDA companies saw plenty of value in the smaller simulation software companies, not to mention the technical ability behind it. For a comparatively small amount of money, an EDA company could dramatically improve its simulation software lineup.

may be too big to be acquired, but you have to wonder whether Mentor, Cadence or Zuken have their eyes on any of the other four.

They'd all be worth acquiring just for the engineering talent alone.

there Still, seems to be a disconnect; some OEMs just don't see any reason to run simulation. I talk with plenty of designers who don't simulate their designs, and these guys aren't designing yesterday's tech-

nology. They're creating some seriously cuttingedge, multigig boards. I've seen stats showing that only about half of all PCB designs are simulated, and that seems pretty accurate to me.

Do you simulate your designs? Send me an e-mail and let me know why or why not. This is definitely a topic worth revisiting.

#### **Happy Birthday**

Before I sign off, I'd like to offer a few birthday wishes. HyperLynx, Mentor Graphics' simulation software tool, is celebrating its 25<sup>th</sup> birthday this year. The company HyperLynx

#### **TO SIMULATE OR NOT TO SIMULATE?** continues

was founded in 1988, aiming to bring highspeed design tools to the then-nascent PC world. The first HyperLynx tool was LineSim, followed by BoardSim and the EMC analysis tool SpectralSim. HyperLynx stayed involved in the industry, and management co-founded the IBIS Open Forum in 1993. In 1997, HyperLynx was acquired by PADS, which in 2000 was purchased by Innoveda. Mentor then acquired Innoveda in 2002. Mentor demonstrated the newest HyperLynx release at DesignCon in January.

And Intercept Technology is turning 30 this year. When Intercept started out as an engineering consulting firm in 1983, founder Steve Klare had no intention of running an EDA software company. But after a decade of dealing with the challenges related to the CAE and CAD software of the time, Intercept began developing its own EDA tools. The company recently redesigned the GUI of its Pantheon design suite, which had remained unchanged,

and still loved by many users, since its introduction in 1994. Intercept now offers solutions for RF and hybrid design, as well as schematic and library management tools.

We always hear that our industry is static, that PCB designers and design engineers are afraid of change. Well, there might be some truth to that. After all, most of us are in our 40s and 50s, and it's only natural that we become set in our ways.

But the industry is constantly changing. And isn't that why we enjoy our jobs in the first place? **PCBDESIGN**

Andy Shaughnessy is managing editor of *The PCB Design Magazine.* He has been covering PCB design for 13 years. He can be reached by clicking <u>here</u>.

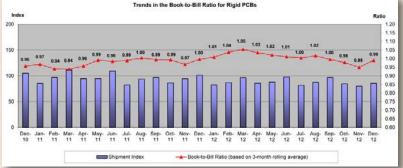

### IPC: December 2012 Shipments, Bookings Down

IPC has announced the December findings from its monthly North American Printed Circuit Board (PCB) Statistical Program.

Rigid PCB shipments were down 16.1% in December 2012 from December 2011, and bookings decreased 8.8% year over year. Year to date, rigid PCB shipments declined 5.5% and bookings decreased 1.7%. Compared to the previous month, rigid PCB shipments were up 7.1% and rigid bookings increased 19%. The book-to-bill ratio for the North American rigid PCB industry in December 2012 recovered to 0.99.

Flexible circuit shipments in December 2012 were up 6.7%, and bookings were up 9.4% compared to December 2011. Year to date, flexible circuit shipments decreased 1.5% and bookings decreased 10%. Compared to the previous month, flexible circuit shipments decreased 7.4%, but flex bookings were up 20.2%. The North American flexible circuit book-to-bill ratio improved to 0.84.

For rigid PCBs and flexible circuits combined, industry shipments in December 2012 were down 14.5% and bookings decreased 7.5%, compared to December 2011. Year to date, combined industry shipments were down 5.2% and bookings were down 2.4%. Compared to the previous month, combined industry shipments for December 2012 increased 5.7% and bookings increased 19.1%. The combined (rigid and flex) industry book-to-bill ratio in December 2012 rose to 0.98.

"North American PCB book-to-bill ratios appear to have begun recovering after a downward trend that began in the second quarter of 2012," according to Sharon Starr, IPC director of market research. "The industry's sales ended 2012 at 5.2% below 2011."

# Measuring Correlation to 50 GHz and Beyond

### by Yuriy Shlepnev

SIMBERIAN INC.

SUMMARY: Four essential elements of electromagnetic signal integrity analysis guarantee successful design of PCB and packaging interconnects up to 50 GHz and beyond: bandwidth and quality of S-parameter models, broadband material characterization and identification, localization of all elements of a channel and systematic benchmarking process. All of these elements of the design flow lead to success, and neglecting or missing even one of them may compromise the whole project.

### Introduction

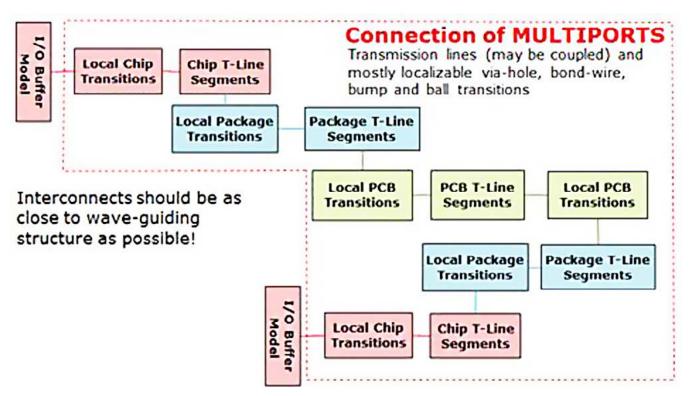

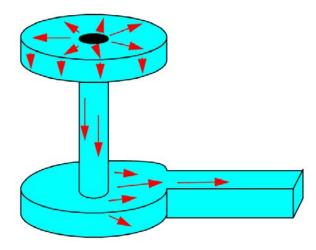

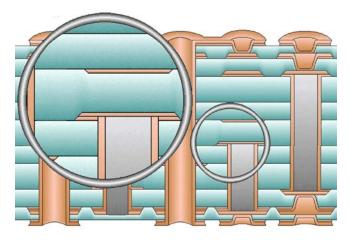

Faster data rates drive the need for accurate models for data channels, specifically for PCB and packaging interconnects. Now, 10 gigabit Ethernet is practically in the mainstream, and 25 gigabit is coming out. The spectrum of signals in these channels ranges from DC or MHz frequencies up to 20-50 GHz and beyond (into centimeter and millimeter wavelengths) and imposes very special requirements on the interconnect modeling and design. Using simplified models or none at all may result in complete failure of such channels and require multiple iterations to fix, and this may be not possible. What is the best way to model such high-speed interconnects? It obviously depends on a problem to solve. For signal integrity analysis, interconnects can be formally divided into transmission line segments (planar or cables) and discontinuities or transitions in lines such as vias and connectors as schematically shown in Figure 1.

**Figure 1:** Interconnect model as connection of multiports. In general, the goal of interconnect design is to make it as close to a localized wave-guiding structure as possible and thus predictable with the analysis.

# PCB MANUFACTURING SUCCESS!

### We Have a Better Way to Predict

DFMStream provides powerful DFM capabilities in an easy-to-use tool suite designed to help engineers and designers verify design and manufacturing rules on PCB design databases, Gerber and NC data any time during the PCB design cycle. DFMStream bridges the gap between engineering and fabrication, helps save valuable time and reduces new product introduction bottle necks.

- Provides powerful DFM functionality

- Easy to learn, even for infrequent users

- Easy to implement as part of the everyday design flow

- Saves time and increases productivity

For more information visit downstreamtech.com or call 800-535-3226

#### Netlist errors are quickly validated in DFMStream

Define DFM checks by area so components such as BGAs can be verified with unique rules different from rest of design

### **MEASURING CORRELATION TO 50 GHZ AND BEYOND** continues

Multiport models of components are built separately with static or electromagnetic analysis, measurements or obtained from component vendors and then united into a complete channel model. This technique was developed from microwave application and is known as decompositional electromagnetic analysis (also known as "divide and conquer" or the segmentation technique). It is also widely used in signal integrity analysis tools for digital applications. Still, the limitations of this technique and key elements that lead to success in the case of digital interconnects is a subject of ongoing research (see the latest DesignCon papers, for instance). Interconnects typically require analysis over a much larger frequency band, and may contain components that have not being used in microwave applications. This article will explain four essential elements of the decompositional electromagnetic signal integrity analysis that guarantee measurement correlation up to 50 GHz and beyond:

- 1) Quality of S-parameter models of interconnects (bandwidth, sampling, passivity and causality).

- 2) Broadband dielectric and conductor roughness models (important for analysis of transmission lines).

- 3) Localization property and de-embedding of discontinuities (possibility to be analyzed in isolation).

- 4) Procedure to validate models with measurements on a set of standard test structures (benchmarking).

#### **Quality of S-parameter Models**

Any element of a linear time-invariant data channel can be modeled as a multiport described with S-parameter models<sup>[1, 2]</sup>. Multiport is a natural and scalable black-box description of linear structures smaller, comparable to, or larger than the wavelength. In decompositional analysis, multiport parameters of transmission lines, via holes and other components are united and then simulated with models of the transmitter and receiver as schematically shown in Figure 1. Multiports are often described with Sparameter models produced by circuit and electromagnetic simulators, VNAs and TDNAs. Very often such models have issues and may be not suitable for consistent broadband frequency, time-domain and compliance analyses of interconnects. Analysis to measurement correspondence is possible only with multiport models that have sufficient bandwidth and pass quality control. This is one of the key elements in the design success.

S-parameter models are usually band-limited due to the limited capabilities of solvers and measurement equipment. Model should include the DC point or allow extrapolation, and high frequencies defined by the signal spectrum. If a model does not contain the DC point, the lowest frequency in the sweep should be below the transition to skin effect (1-50 MHz for PCB applications), or below the first possible resonance in the system defined as

$$f_l < \frac{c}{4L \times \sqrt{\mathsf{e}_{eff}}}$$

to allow extrapolation to DC. Here L is total physical length of the system, c is speed of light and  $e_{eff}$  is effective dielectric constant. The highest frequency in the sweep must be defined by the required resolution in time-domain or by spectrum of the signal<sup>[4]</sup>. The highest frequency can be defined either with signal rise time tr as

$$f_h > \frac{1}{2t_r}$$

or with the main harmonic fs1 as

$f_h > K \times f_{s1}$ .

Here K may range from 2 to 5, depending on the actual attenuation in the channel. All models for a channel interconnects should satisfy the target bandwidth requirement. Otherwise they have to be discarded and rebuilt.

In addition to being band-limited, most interconnect component models come in the form of Touchstone models<sup>[3]</sup>. Touchstone models are just S-parameters defined at a set of frequencies. Interpolation or approximation of tabulated matrix elements may be necessary both for timeand frequency-domain analyses. Appropriate sampling is very important for DFT and convo-

#### **MEASURING CORRELATION TO 50 GHZ AND BEYOND** continues

lution-based time domain analysis algorithms<sup>[4]</sup>, but not so for algorithms based on rational approximation. In general, there must be 4-5 frequency points per each resonance. In addition, the electrical length of a system should not change more than one quarter of wavelength between two consecutive frequency points

$$df < \frac{c}{4L \times \sqrt{\mathsf{e}_{eff}}}$$

Under-sampling typically occurs at lower frequencies and may lead to defects both in frequency and time-domain analyses. Such models have to be discarded and rebuilt.

On top of being band-limited and the risk of possible undersampling, these models can be distorted with the measurement or simulation artifacts that are not so easy to detect. For instance, model convergence issues, fast frequency sweeps, non-conservative ports, and unaccounted high-order modes in electromagnetic analysis may cause model distortions. Measurement noise, calibration and measurement equipment problems can also lead to defective models. In general, those are human mistakes of tools developers and users.

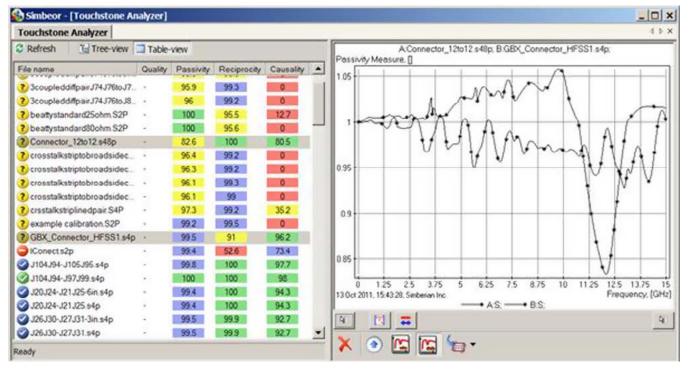

How best to estimate the quality of S-parameter models to make sure that the models are suitable for analysis? S-parameters quality metrics have been recently introduced<sup>[5, 6]</sup> to simplify the task. Metrics for passivity, reciprocity and causality computed for band-limited discrete models can be used for preliminary analysis of the quality of S-parameters. The metrics range from 0 to 100; zero means bad and 100 is good. Ranges for acceptable and questionable models are defined on the base of analysis of thousands of models. An example of preliminary analysis of a set of models in Simbeor Touchstone Analyzer tool<sup>[7]</sup> designed for automation of S-parameter quality assurance is shown in Figure 2.

Note that preliminary quality estimation is done for a discrete and band-limited data set and, thus, is incomplete. Though, it allows detecting unacceptable violation of passivity and reciprocity. If passivity or reciprocity metrics are close to zero, the model must be discarded and

**Figure 2:** Example of preliminary analysis of Touchstone models quality in Simbeor Touchstone Analyzer. Good metrics are shown in green; acceptable in blue; questionable in yellow; and bad is red. Graph on the right is adjusted for passivity measure for two selected models – passivity violated if the measure is above unit.

rebuilt. Large violations of preliminary causality metric in computed models point at undersampled data – such models have to be also rebuilt. Large causality violation in measured data may occur because of measurement noise and can be fixed with the rational approximation. A model ranked as good with preliminary metrics may still have hidden defects and may not allow accurate interpolation or extrapolation for purpose of time-domain analysis for instance. Rigorous estimation of passivity and causality can be done only for a frequency-continuous model defined from DC to infinity. Such models can be built with the rational approximation of the original tabulate data.

Rational macro-models are frequency-continuous models defined from DC to infinite frequency and can be used for the final quality estimation. High-quality tabulated models can be accurately approximated with passive rational macro-models. The final quality metric with a range from 0 to 100 can be constructed using the root-mean square error (RMSE) of the passive rational approximation as<sup>[6]</sup>

$$Q = 100 \cdot \max(1 - RMSE, 0)\%$$

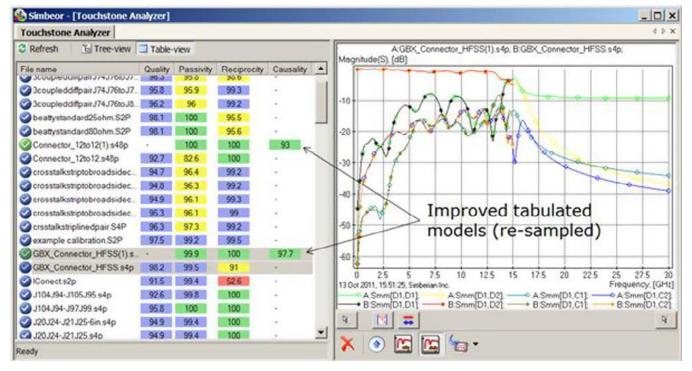

S-parameters approximated with rational functions are causal by definition in case passivity is ensured from DC to infinite frequencies. An example of the final model quality estimation with rational macro-models is shown in Figure 3. Low-quality metrics mean that the tabulated model cannot be accurately interpolated and extrapolated with a causal passive model and must be discarded. After model quality is ensured, it can be further exported and used as a broadband SPICE macro-model (BB SPICE) or improved by resampling. Note that BB SPICE models are frequency-continuous and contain extrapolation to DC and infinity and, thus, guarantee consistent analyses both in frequency and time-domain in practically all tools.

### Broadband Dielectric and Conductor Roughness Models

The largest part of interconnects can be formally defined and simulated as transmission

**Figure 3:** Example of the final model quality analysis in Simbeor Touchstone Analyzer. Model icons and the "Quality" column illustrate the model quality estimated with the passive rational approximation (good = green, blue = acceptable). Columns passivity and reciprocity show quality of the original tabulated data. Graph on the right is adjusted to compare magnitudes of the original and "improved" models.

### Murrietta Circuits: The Integrated Solution Everything you need, from one company.

When you need quality, reliable Flex and Rigid Flex on-time and on-budget, look no further than **Murrietta Circuits!**

- Single & Double Sided Flex

- Flex with Stiffeners

- Rigid-Flex

- 1-24 Layer

- Controlled Impedence

- Blind/Buried Vias

- Loose Leaf, Bonded & Staggered Flex

- Coverlay & Flexible Mask

It's all here under one roof ...why go anywhere else?

The future of Electronic **Manufacturing Services (EMS)** -here today.

5000 East Landon Drive, Anaheim CA 92807 (714) 970-2430 | sales@murrietta.com | www.murrietta.com

line segments. Models for transmission lines are usually constructed with static or electromagnetic field solvers. Transmission lines with homogeneous dielectrics (striplines) can be effectively analyzed with quasi-static field solvers, and lines with inhomogeneous dielectric may require analysis with a full-wave solver to account for the high-frequency dispersion<sup>[8, 9]</sup>. Accuracy of transmission line models is mostly defined by availability of broadband dielectric and conductor roughness models. Wideband and multipole Debye models<sup>[9]</sup> are examples of widely used dielectric models suitable for accurate analysis of PCB and packaging interconnects. Parameters for such models are usually not available from manufacturers and have to be identified.

To simulate the effect of conductor roughness, modified Hammerstadt<sup>[10]</sup> and Huray's snowball conductor roughness models<sup>[11]</sup> can be used effectively, but parameters for such models are not readily available from manufacturers. Makers of dielectrics provide dielectric parameters at 1-3 points in the best cases; those points may be acceptable to define a wideband Debye model. Copper laminate manufacturers

typically do not offer parameters for electrical roughness models. Thus, meaningful interconnect design and compliance analysis must start with the identification or validation of dielectric and conductor roughness models over the frequency band of interest. Even electromagnetic analysis of interconnects without such models may simply be inaccurate and useless.

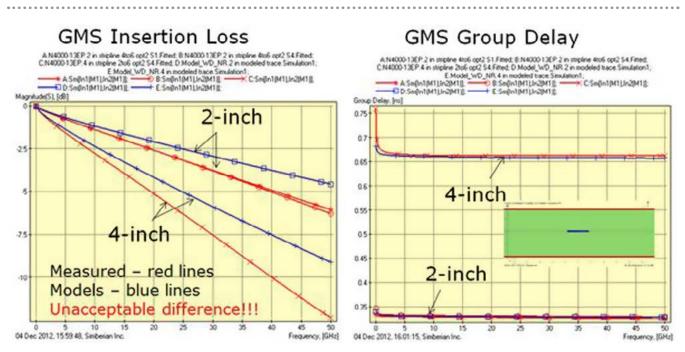

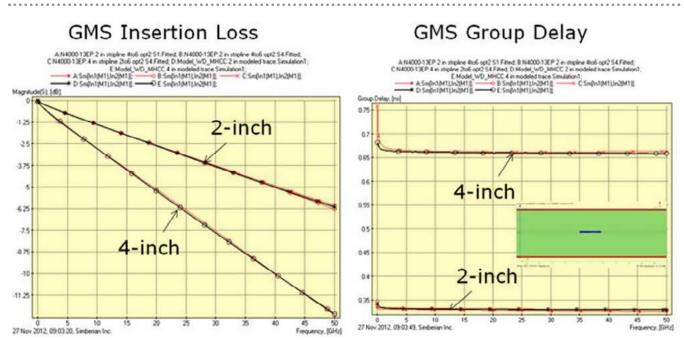

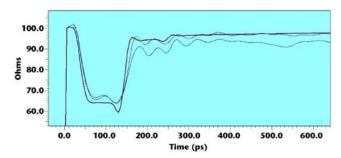

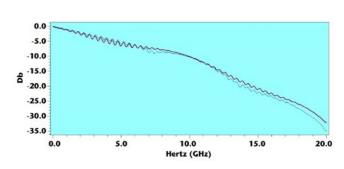

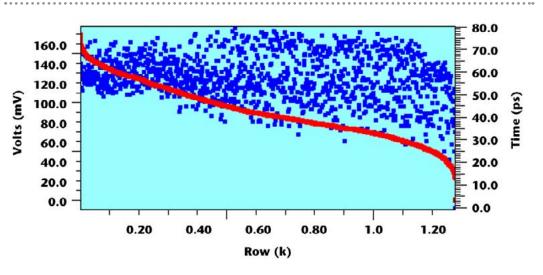

Accurate material characterization up to a target frequency is the most important element for design success. The simplest procedure for such validation or identification is based on generalized modal S-parameters (GMS-parameters)<sup>[12]</sup>. S-parameters are measured for two line segments with substantially identical transitions and cross-sections, converted into reflectionless GMS-parameters, and material models are then identified by matching computed and measured GMS-parameters. The procedure is automated in Simbeor software. As an example of material parameters identification up to 50 GHz (for 25-30 Gbps data channel), we use measured data provided by Molex engineer David Dunham for one of the material characterization boards made of Nelco N4000-13EP dielectric and VLP copper<sup>[13]</sup>. A set of 2-, 4- and

**Figure 4:** Measured (red lines) and computed (blue lines) generalized modal insertion loss (left plot) and group delay (right plot) for 2- and 4-inch strip line segments (dielectric model from manufacturer and smooth conductor model).

6-inch stripline segments was used to extract reflectionless GMS-parameters for 2-inch and 4-inch line segments as shown in Figure 4. The dielectric specifications show that this dielectric may have dielectric constant (Dk) from 3.6 to 3.7 and loss tangent (LT) from 0.008 to 0.009.

If we compute GMS-parameters for 2- and 4-inch segments using electromagnetic analysis with a wideband Debye model and Dk=3.8 and LT=0.008 defined at 10 GHz, the difference in the measured and computed group delay is very small, but the difference in GM insertion loss is huge, as illustrated in Figure 4. Dk in the model is slightly increased to match group delays – that increase can be explained by anisotropy of the dielectric. Horizontal component of the Dk for layered glass-resin dielectrics can be up to 20% larger<sup>[14]</sup> and the manufacturer probably used wider strips to identify the dielectric. Wider strips have less energy in the horizontal component of electric field and predict smaller Dk.

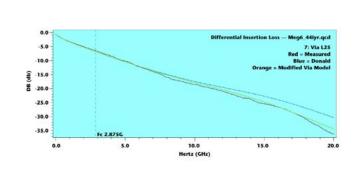

What about the loss tangent – how can we explain such huge difference in the predicted and measured IL? Typically this situation is explained as wrong data provided by the manufacturer. In this case LT should be increased to 0.0112 to have an acceptable match for insertion loss. Another option is to assume that the dielectric data from the manufacturer are actually correct, and attribute all observed excessive losses to the conductor roughness. As shown in Figure 5, nearly perfect correspondence of measured and computed models can be achieved with the modified Hammerstadt model with a roughness parameter of 0.27, roughness factor of 4 and conductor resistivity adjusted to 1.1 (relative to resistivity of annealed copper).

As the result of this simple example we ended up with two models – with LT=0.0112 and no roughness and with LT=0.008 (as in the specs) and additional model for conductor roughness. Which one is correct? Both models are suitable for the analysis of the 8.5 mil stripline on this board. However, if strips with different width are used, the model without the roughness model will be much less accurate. For instance, the model without roughness predicts up 40% smaller losses for differential strip with 4 mil wide strips and 4 mil spaces. The model with the rough conductor is expected to produce more accurate insertion loss estimation for a broad range of strip widths. This example illustrates a typical situation and the im-

**Figure 5:** Measured (red lines) and computed (black lines) generalized modal insertion loss (left plot) and group delay (right plot) for 2- and 4-inch strip line segments (dielectric model from manufacturer and rough conductor model with SR=0.27, SR=4).

portance of dielectric and conductor roughness model identification to measure correspondence for a set of transmission lines on a particular board for a target frequency range.

### Localization Property and De-Embedding Discontinuities

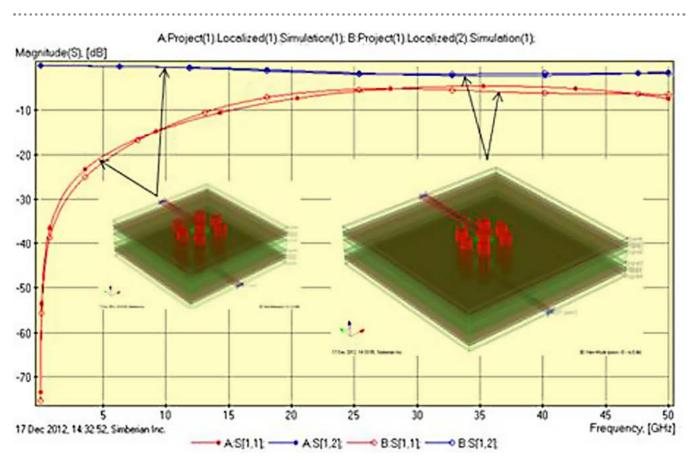

Ideally, all interconnects should look like uniform transmission lines with specified characteristic impedance. In reality, a channel is typically composed of transmission lines of different types (microstrip, stripline, coplanar, coaxial, etc.) and transitions between them such as vias, connectors, breakouts and so on. Even if we maintain the same impedance for lines of different types, the transitions may be still reflective due to physical differences in crosssections of the connected lines (coaxial and micro-strip for instance). The reflections cause additional losses and resonances and, thus, unwanted signal degradation. The effect of the transitions can be accounted for with models built with a full-wave 3D analysis. If such analysis is possible in isolation from the rest of the board up to a target frequency, the structure is called localizable<sup>[15]</sup>. Structures whose behavior is dependent on board geometry are called not localizable, and they should not be used for multi-gigabit interconnects in general. Analysis of such structures is possible only at the postlayout stage with substantial simplifications that degrade accuracy of the model at frequencies above 3-5 GHz. In other words, only localizable transitions and discontinuities must be used to design predictable interconnects at frequencies above 3-5 GHz - this is one of the most important elements of successful design.

How best to estimate the localization property of a transition? The simplest way is to run electromagnetic analysis of the structure with different boundary conditions or simply change simulation area size and evaluate the differenc-

**Figure 6:** A localization property evaluation for a single via with six close stitching vias. Increase of simulation area size just slightly changed computed reflection (red lines) and insertion loss (blue lines).

### **MEASURING CORRELATION TO 50 GHZ AND BEYOND** continues

es. An example of the localization evaluation for a single via with six stitching vias is shown in Figure 6. The structure can be considered as localizable up to 50 GHz. The via in this example is localizable, but not optimal – the reflection loss may be not acceptable if multiple vias are used in a channel. Further via optimization can be performed in Simbeor Via Analyzer and SiTune optimization tools.

In this comparison of S-parameters of two vias simulated in different area, de-embedded transmission line ports are used to reduce the numerical reflection and to shift the phase reference plane closer to vias and to have S-parameters describing exactly the same portion of the geometry. The quality of such numerical de-embedding defines the quality of the final interconnect model. The simplest way to evaluate the de-embedding quality is to simulate a 90-degree segment of ideal 50-ohm stripline as suggested here<sup>16</sup>. This simple test allows rigor-

ous estimation of de-embedding accuracy and dynamic range. Another way is to simulate a T-line segment and concatenate the models into a longer segment – there should not be reflections observed at the connection points. If substantial reflections observed in such numerical experiment, the models are not suitable for the decompositional analysis.

### Analysis to Measure Validation – Benchmarking

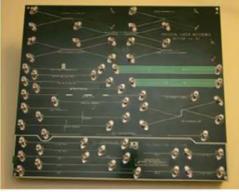

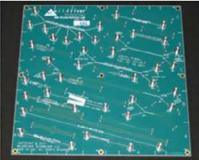

Finally, how to make sure that the interconnect analysis works up to the target frequency and what is the problem if it does not? The best way to evaluate the accuracy of analysis is to build a validation or benchmarking board and compare analysis results with measurements. Benchmarking is one of the most important elements of the design success. First of all, such board should include a set of structures to identify all dielectrics and conductor roughness

PLRD-1 (Teraspeed Consulting, DesignCon 2009, 2010)

Isola, EMC 2011, DesignCon 2012

CMP-08 (Wild River Technology & Teraspeed Consulting, DesignCon 2011

CMP-28, Wild River Technology, DesignCon 2012

**Figure 7:** Examples of benchmarking boards featured in References 12 and 17 (top left), Reference 18 (top right), Reference 19 (bottom left), and Reference 20 (bottom right).

### **MEASURING CORRELATION TO 50 GHZ AND BEYOND** continues

models. There must be at least one pair of lines per material model to separately identify models for solder mask, core and prepreg dielectrics or resin and glass, conductor roughness, plating material and so on. Identification of two models at the same time may lead to multiple possibilities and is problematic, as was pointed out at the dielectric and roughness model identification section. Benchmarking should also include a set of structures to identify the accuracy for transmission line models with possible coupling, resonant structures (i.e., Beatty standards or other type of planar resonators) and typical discontinuities (channels with single and differential vias, for instance). Examples of benchmarking boards<sup>[12, 17, 20]</sup> developed and investigated up to 50 GHz are shown in Figure 7.

Considering the benchmarking process, identified material models must be consistently used for the analysis of all structures on the board. Tweaking dielectric or conductor roughness models for each structure for instance should be strictly prohibited. Possible discrepancies reveal either limitations of a tool or board design or manufacturing defects that altered the expected behavior. The source of the discrepancy must be investigated. The best choice for benchmarking measurement is VNA with the target frequency bandwidth. Either coaxial connectors or probe launches can be used. Probe launches are easier to model, but the measurement have to be done with a probe station - handheld probes are simply not suitable at microwave frequency range.

In the case of connectors with launches, they can be de-embedded or simulated too (more difficult due to unknown material properties). TRL-type de-embedding can be used for PCBs<sup>[17]</sup>, but additional structures may be needed for the de-embedding (they can be also used for the material parameters identification). Note that simple T-matrix de-embedding simply does not work for PCB applications due to inhomogeneity of dielectrics and large manufacturing variations. Finally, measured and computed magnitudes and phases or group delays for all S-parameters have to be compared. Just insertion loss comparison is incomplete and may be misleading. Always compare phase or group delay and also reflection parameters.

#### Conclusion

Four essential elements that guarantee successful design of PCB and packaging interconnects up to 50 GHz and beyond have been outlined in this article. Bandwidth and quality of S-parameter models, broadband material characterization and identification, localization of all elements of a channel and systematic benchmarking process are equally important elements of successful design. If even one element is missing or neglected, it may compromise the whole project. **PCBDESIGN**

### References

1. H. J. Carlin, A. B. Giordano, Network theory: An introduction to reciprocal and nonreciprocal circuits, Prentice Hall, 1964.

2. J. Choma, Electrical networks: Theory and analysis, John Wiley & Sons, 1985.

3. IBIS Open Forum Touchstone File Format Specification <u>www.eda.org/ibis/</u>

4. P. Pupalaikis, The Relationship Between Discrete-Frequency S-Parameters and Continuous-Frequency Responses, DesignCon 2012.

5. Y. Shlepnev, Quality Metrics for S-parameter Models. IBIS Summit at DesignCon 2010, www.eda.org

6. Y. Shlepnev, Reflections on S-parameter Quality, IBIS Summit at DesignCon 2011, <u>www.</u>eda.org/ibis/

7. Simbeor Electromagnetic Signal Integrity Software, <u>www.simberian.com</u>

8. Y. Shlepnev, Modeling frequency-dependent conductor losses and dispersion in serial data channel interconnects, Simberian App. Note #2007\_02, <u>www.simberian.com</u>

9. Y. Shlepnev, Modeling frequency-dependent dielectric loss and dispersion for multigigabit data channels (with experimental validation), Simberian App. Note #2008\_06, <u>www.</u> <u>simberian.com/AppNotes</u>

10. Y. Shlepnev, C. Nwachukwu, Roughness characterization for interconnect analysis. -Proc. of the 2011 IEEE International Symposium on Electromagnetic Compatibility, Long Beach, CA, USA, August, 2011, p. 518-523.

11. P. G. Huray, O. Oluwafemi, J. Loyer, E. Bogatin, X. Ye, Impact of Copper Surface Texture on Loss: A Model that Works, Design-Con 2010.

### **MEASURING CORRELATION TO 50 GHZ AND BEYOND** continues

12. Y. Shlepnev, A. Neves, T. Dagostino, S. McMorrow, Practical identification of dispersive dielectric models with generalized modal S-parameters for analysis of interconnects in 6-100 Gb/s applications. DesignCon 2010.

13. D. Dunham, J. Lee, S. McMorrow, Y. Shlepnev, 2.4mm Design/Optimization with 50 GHz Material Characterization, DesignCon2011.

14. M.Y. Koledintseva, S. Hinaga, and J.L. Drewniak, "Effect of anisotropy on extracted dielectric properties of PCB laminate dielectrics", IEEE Symp. on EMC, Long Beach, CA, Aug. 14-19, 2011, pp. 514-517.

15. Y. Shlepnev, Designing localizable minimal-reflection via-holes for multi-gigabit interconnects, Simberian App. Note #2009\_05, <u>www.</u> <u>simberian.com/AppNotes.php</u>

16. J.C. Rautio, An ultra-high precision benchmark for validation of planar electromagnetic analysis, IEEE on MTT, v.42, N11, 1994, p. 2046-2050.

17. Y. Shlepnev, A. Neves, T. Dagostino, S. McMorrow, Measurement-Assisted Electromag-

netic Extraction of Interconnect Parameters on Low-Cost FR-4 boards for 6-20 Gb/sec Applications, DesignCon 2009.

18. J. Bell, S. McMorrow, M. Miller, A. P. Neves, Y. Shlepnev, Unified Methodology of 3D-EM/Channel Simulation/Robust Jitter Decomposition, DesignCon 2011.

19. Y. Shlepnev, C. Nwachukwu, Practical methodology for analyzing the effect of conductor roughness on signal losses and dispersion in interconnects, DesignCon 2012.

20. CMP-28 Channel Modeling Platform, Wild River Technology, <u>wildrivertech.com/</u>

Yuriy Shlepnev, Ph.D., is founder and president of Simberian Inc. He previously served as principal engineer at Mentor Graphics and director of the Electromagnetic Group at Eagleware Corporation.

### video Interview

### Simberian: High-End Simulation For Designers

### by Real Time with... PCBDesign007

Yuriy Shlepnev discusses his latest release, Simbeor 2013. Simbeor did not win a Design Vision Award at Design-Con this year, but Simbeor has already taken home the award two years in a row. Shlepnev also shows off one of his latest projects.

### CONNECTING THE DOTS

### PCB Design Data: What Do Your Customers Expect?

### by Jack Olson

SUMMARY: What does a circuit board designer produce? Who are our customers, and what do they expect from us? Here's a brief description of the types of data you will be providing during various stages of the electronics development process.

One vision for the future of our industry is that every CAD system would have

the ability to output a common file format. Imagine a single file that could be sent to all of our customers, and each would extract the type of data needed for a specific process. A universal data format for electronics manufacturing will offer many advantages, and many are diligently working toward that goal; however, several considerations still need to be resolved, and there is still no consensus yet among industry leaders.

In the meantime, you need to know what you will be creating for

your customers. The end result will be two major sets of manufacturing data: one for bare board fabrication and the other for assembly and test. In addition to these two, you may also be asked to provide other files along the way, so let's take a look at those first.

#### **Bill of Materials (BOM)**

When packaging a design, your CAD software will interpret the schematic diagram and map the symbols into components, assigning a unique identifier called a reference designator to each one. Since the system now knows how many of each type of component is required to build the product, a part list or bill of materials (BOM) can be generated.

Even before you start the board layout, several people may be waiting for the BOM infor-

mation, so don't delay sending it. The people responsible for purchasing may want this information to start looking for components that have long buying lead times, or for cost analysis or inventory control, and maybe even for component obsolescence study. Once you are confident that your BOM matches the design intent, get it to the people who can use it as soon as possible.

#### **Mechanical Data**

CAD systems used for circuit board layout are usually different than the CAD systems used to design the mechanical aspects of the product,

but if a common file format can be used to transfer data between them, your job may get a lot easier.

Since physical details of the product such as the dimensions of the enclosure or the mounting scheme are most often defined in a mechanical CAD system, it may be easier for a mechanical engineer to define the board outline and send it to you. This process can become quite sophisticated, including the abil-

" Providing Solutions to Board Fabrication Challenges"

# FROM CONCEPT TO COMPLETION

### **Solutions for Every Complex Situation**

At Multilayer Technology we have the skills and the knowledge to be able to say "Yes We Can!" to your most complex design requirements.

We specialize in High-Speed Digital and RF Design constraints. In addition, we offer the following solution-based services:

- Extensive Exotic Material Processing

- Pre-DFM Services Available

- State-of-the-Art Industry Leading Processes

- Space-Based Reliability Requirements Standard

**REQUEST A QUOTE**

WWW.MULTILAYER.COM

Multilayer Technology 3835 Conflans Rd Irving, TX 75061-3914

(972) 790-0062

Mil-PRF-55110

### PCB DESIGN DATA: WHAT DO YOUR CUSTOMERS EXPECT? continues

ity to define keep-out areas, height restrictions, connector locations, mounting hole sizes, etc. Importing this type of data directly into the circuit board layout can save time and reduce the chance for errors and oversights.

If the circuit board layout software can export a file back to the mechanical design software, additional interference checks can be performed before manufacturing begins. Sometimes a 3D model can be created in the mechanical system, and seeing a better representation of your final assembly mounted inside the product can highlight an issue that might not have been apparent in your 2D layout software, so take advantage of it if it is available.

### Quoting

Before the design is finished, the purchasing department may ask you in advance for enough information to get a budgetary quote. The fabrication data and drawing will provide everything a bare board fabricator needs to know about the product, but these can't be created before the layout is complete. In the meantime, cost analysis and purchase orders can start if you can provide the basic parameters of the design. For the bare board quote, they will want to know:

- Board size, thickness, and any cut-out or slot requirements.

- Board material including desired final finish.

- Number of layers.

- Approximate number of holes, and smallest hole size.

- Smallest trace width and clearance.

- Quantity of boards and required turnaround time.

Some of these estimates change slightly before the design is finished, but most fabricators are willing to provide a budgetary quote as long as they can adjust the price if there are significant changes.

### The Fabrication Data Package

### Artwork

You will be providing a description of each layer image either in Gerber format or in one of

the other proprietary data formats supported by your CAD system.

Most circuit board artwork is described using the Gerber data format, so I should probably include a little historical background before we move on. The Gerber data format was developed by Gerber Scientific in 1980 as an input to control a photoplotter. A photoplotter was similar to a pen plotter, but instead of using ink on paper it used different sized apertures to expose an image on film, using a beam of light. Each file describes a single layer, and is used to create images for conductive layers, soldermask layers, silkscreen layers, and paste screen layers. These layers were created by flashing exposures in specific locations defined by shape (circles to create plated through-hole pads, for example, or rectangles to create SMT lands, etc.) and connecting them together by drawing exposures from point to point with apertures specified by width (usually round).

When using the original Gerber format (based on a subset of EIA RS-274-D), an aperture list was also required to define the sizes of the draws and flashes, but Gerber data files created using the newer RS-274-X format have the aperture information embedded in each file, so a separate list is not required. Use the newer 274X format if your CAD system can support it.

Although the Gerber data format was developed to control a photoplotter using draws and flashes, modern CAM systems can read in all the data at once and rasterize a complete image for each layer. This is much faster than drawing/ flashing each feature sequentially.

### **Drill Data**

Two more types of ASCII files are needed for numerically controlled drilling (NCD). These will be used to define the size and location of all the holes in the circuit board, both plated and unplated.

- A tool table lists the diameter of each drill size and assigns them to tool numbers, and gives instructions about how to interpret the drill data.

- The drill data file contains hole locations for each drill sorted by tool number.

### PCB DESIGN DATA: WHAT DO YOUR CUSTOMERS EXPECT? continues

As a supplement to the ASCII drill data files, it is customary to provide additional information related to drilling on the fabrication drawing in the form of a hole legend or drill chart. During quoting, and for quality inspection activities, this summary is easier to read than having to interpret the raw data. Drill sizes are given unique symbols or letters, and the pic-

torial representation of the board on the drawing will show these symbols as a visual aid.

#### Netlist

The netlist file is not always included in fabrication data packages, but it probably should be. A bare board can be fabricated without a netlist, but if it is available, an extra level of checking is available that can help ensure that the data files describe the intended connectivity. This file should be in the IPC-D-356 format, which can be created automatically by most PCB layout software packages.

### **Fabrication Drawing**

The fabrication drawing fulfills several important functions to support the circuit board manufacturing process:

- It provides enough information about the design for the bare board fabricator to prepare a quote.

- It adds all the extra details about the build that aren't easily incorporated into the data files, like material and final finish.

- It lists the criteria by which the finished product will be evaluated for acceptability.

- It serves as a tool to be used during final inspection.

- It is a record or document to store the history of a product by title, part number and revision, physical dimensions, and lists the name of the designer and possibly several other supporting entities as well as the company name and address, etc.

As a supplement to the ASCII drill data files, it is customary to provide additional information related to drilling on the fabrication drawing in the form of a hole legend or drill chart.

Several different types of information can be found on a typical fabrication drawing: board details including layer stack-up and construction, materials and process specifications, conductor width and clearance minimums, fabrication allowances, impedance requirements, marking requirements, test coupon requirements, performance requirements, and

a graphical representation of the board with critical dimensions.

#### ReadMe.txt

Including this file into your data package gives you an opportunity to add extra information to the bare board fabrication order. For example, you may have intentionally shorted two nets together (like AGND and DGND) and you don't want the fabricator to put your job "ON HOLD" because of a netlist discrepancy. A README.TXT file is the place to include additional notes that you may not want to show in the

final documentation. This is also a good place to list yourself or someone else as a

contact, with name, phone number and e-mail address.

### The Assembly/Test Data Package

#### **Assembly Drawing**

The centerpiece of an assembly drawing is a pictorial representation of what the finished electronic assembly will look like. The graphics should clarify component polarity, and provide other details specific to the assembly. Notes can be added for any special instructions and to indicate what level of workmanship and acceptability is expected.

### **Solder Paste Data**

If surface mount components are used in the design, they will be attached to the board using solder paste. This solder paste is applied to the surface of the board using a stainless steel paste screen, which is typically created using a Gerber data file that describes the areas of the

### PCB DESIGN DATA: WHAT DO YOUR CUSTOMERS EXPECT? continues

board where paste is needed. Two paste screens are required if there will be surface mount parts on both sides of the board assembly.

Paste screen technology is quite sophisticated, and unless you really know what you're doing, you should provide paste screen apertures that are the same size as the lands you will be soldering to. This will give the paste screen manufacturer a known starting place to begin making modifications for various technologies.

### **Component Placement Data**

Components needed for the assembly are purchased in quantity, loaded onto reels or inserted into plastic tubes. A component pickand-place machine features a specific number of feeders that are loaded with these tubes and reels. After solder paste is applied to the land patterns of a bare board, it is loaded into the pick-and-place machine where a camera aligns the board using metal targets called fiducials (usually round dots 1 mm in diameter etched into the surface conductor layer). Then components are picked up one at a time and placed on the board in specific locations, at the proper rotation. An ASCII data file contains the fiducial locations, and the X-Y coordinates and rotation for each component.

### ReadMe.txt

This is the place to include additional notes that you may not want to show in the final documentation. This is also a good place to list yourself or someone else as a contact, with name, phone number and e-mail address.

### Test Data

Some products will be manufactured in a high enough volume to make the expense of an in-circuit test (ICT) fixture worthwhile. An ICT fixture and program will be developed to test the final assembled circuit board before it is mounted into the product. For these products you will add test points to the board layout, and then generate an extra file containing the test point coordinates. Many CAD systems can help automate this task. A copy of the schematic may also be helpful for the person developing the test program.

### **Compressed Archives**

Data files are often combined and compressed into a single file called an archive, using a file extension such as ZIP, RAR or TAR. The resulting archive file can be transferred between customers and suppliers, and the individual files can be easily restored at the destination. Three of the most important advantages of compressed archives are:

- Compressed archives keep necessary components of a package together, making organization easier and reducing the chance of missing files.

- Compressed files are much smaller, needing less storage space, less time and less network usage for transfers.

- The software that compresses and uncompresses archives has automatic built-in error checking.

Unless your CAD system can output a single file format that is supported by your manufacturing process, you will probably be combining several different types of data into ZIP files before sending them out to your manufacturing partners.

### Milestones

Throughout the design process there will be several different people using your data. After you work through a few designs, start recording the steps that you did to get from start to finish, and who needed what along the way. Then rearrange the steps where possible to get the data to the people who need it as soon as possible. You don't want to create bottlenecks for others, and it's better for you to be waiting on them than it is for them to be waiting on you. **PCBDESIGN**

Jack Olson, C.I.D.+, has been designing circuit boards fulltime for more than 20 years. He would like to thank all the friends and colleagues who have taken time to teach him about the real world of elec-

tronics development.

### video interview

### **Cadence Integrates Sigrity Capabilities**

### by Real Time with... PCBDesign007

Brad Griffin, product marketing director for Cadence Design Systems, discusses the company's acquisition of Sigrity, as well as the fairly seamless blending of the two companies' cultures.

realtimewith.com

### 2013 DesignVision Award Winners Recognize Innovation

UBM Tech has announced the names of the 2013 DesignVision Award winners, including industry firms Mentor Graphics, TE Connectivity, ANSYS Inc., Upverter, MicroSemi, Teledyne LeCroy and Averna. DesignCon evaluated products from hundreds of exhibitors to choose the winners, who were recognized at an awards ceremony at DesignCon 2013 in Santa Clara, California.

Winners were selected based on three criteria: how well the product met the market's vision and offered unique insight into customer

needs; the originality of the solution and if it offered a new approach to meeting market needs; and the quality of the implementation and how well it fits the market requirements.

The 2013 DesignVision winners by product category are:

- Mentor Graphics, Tessent IJTAG IC Design Tools Category

- TE Connectivity, STRADA Whisper -Interconnect Technologies and Components Category

- ANSYS Inc., HFSS (for ECAD with Cadence)

Modeling and Simulation Tools Category

- Upverter, Upverter PCB Design Tools Category

- MicroSemi, SmartFusion2 Semiconductor Components and ICs Category

- Teledyne LeCroy, HDO High Definition Oscilloscopes - Test & Measurement Category

- Averna, Proligent Analytics 6.0 Verification Tools Category

"We had quite a challenging time choosing these winners among all of the innovative products we judged," said Patrick Mannion, Content Director and Brand Director EDN, Test & Measurement World & Planet Analog. "Ultimately, our 2013 winners represent the best of the best in each of their respective industries."

# Postmortem Simulation

by Barry Olney IN-CIRCUIT DESIGN PTY LTD

SUMMARY: Developing the practice of performing a postmortem analysis on every project facilitates a culture of continuous improvement. This embedded culture of ongoing, positive change is the best way to ensure long-term success.

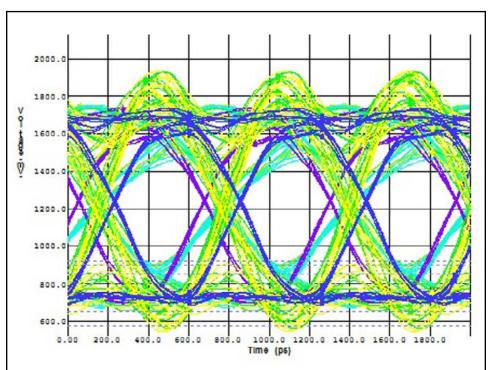

Often we find that PCB simulation is engaged too late in the design cycle. This results in the simulation process becoming more a post-mortem to uncover what has gone wrong with the design and how it can be resurrected to work as intended.

In my work as a high-speed analyst, I sometimes get called on to fix problems that could have been prevented. However, a total disaster can usually be avoided and final success achieved (providing the conceptual design has been validated).

Ideally, every high-speed design should be exposed to the preventative medicine of prelayout simulation and proactive stackup and power-delivery optimization.

As with any forensic postmortem, a thorough external examination is undertaken to see if there are any visible signs of impairment that may identify the cause of the problem. This is what I refer to as "eyeballing" the design. It is actually amazing what can be picked up just by looking closely at the PCB database. I think we have all experienced the case where we simply cannot see the obvious because we are intimately involved in the design – that is, our subconscious does not warrant rechecking the obvious. That is why I always advocate having a second, equally qualified person thoroughly check a PCB before handover to manufacturing.

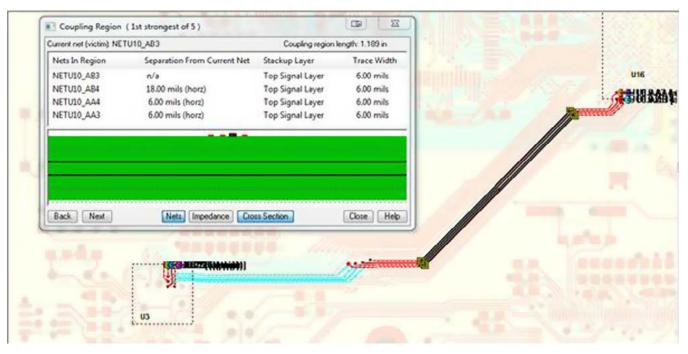

The following is a short list of issues to regularly check in a design:

- Minimum edge/tooling hole clearances and component to edge of board clearance.

- Thermal reliefs are not compromised.

- Split planes (if present) are correctly placed.

- No critical nets cross split planes.

- No critical (high-speed) nets in the analog areas.

- Critical nets must not change reference planes unless accompanied by a stitching via or bypass capacitor.

- Matched length signals memory data, strobe, clock, address, control and command signals are routed to specs.

- All critical nets are buried between solid planes. The allowable length of the exposed portion of a critical net is limited.

- All critical nets must be routed with adequate clearance to avoid crosstalk.

- All power and ground traces longer than 500 mils must be wide enough to carry the specified current.

Toll Free: (888) 995-5171 www.epectec.com

> Stay Connected 🕒 🗗 in 👥 🔛

▶ DELIVERING QUALITY SINCE 1952.

InstantPCBQuote fast.easy.24/7.

### QUOTE & ORDER YOUR RIGID PCBs ONLINE

Our dynamic online PCB quoting program allows you the option of designing the rigid printed circuit board that you need, not the one we want to build. Build your quotes online 24/7 at your convenience. Every quote created is saved in your InstantPCBQuote™ profile, which can easily be viewed, compared, ordered, and re-ordered at any time.

- Quote and Order From 1-16 Layers

- 24 Hour Quick Turn PCB Orders

- Pricing is Available for 1-20 Day Deliveries

- Variety of Laminates and Surface Finishes

- No Minimum Quantities

- Prototype to Production Size Order

**TRY IT NOW!**

www.InstantPCBQuote.com

45-000-REV A

CIRCUIT

### InstantFLEXQuote... fast.easy.24/7.

### QUOTE & ORDER YOUR FLEX PCBs ONLINE

Our online flex circuit quote and ordering tool is a must see for anyone in the industry who deals with flexible PCBs. There are not many other online sites designated for flexible circuits on the Internet with the capability to quote and order flexible circuit boards up to 4 layers.

- Quote and Order From 1-4 Layers

- 7 Day Quick Turn Flex PCB Orders

- Pricing is Available for 7-20 Day Deliveries

- Variety of Materials and Coverlay Options

- No Minimum Quantities

- Prototype to Production Size Order

**TRY IT NOW!** www.InstantFLEXQuote.com

Epec Engineered Technologies • 174 Duchaine Blvd. • New Bedford, MA 02745

### **POSTMORTEM SIMULATION** continues

- All oscillators must be placed within 500 mils from the clock driver.

- Critical nets are not within 3x trace width of the edge of their reference plane.

- Decoupling capacitors are placed within 500 mils from each IC power pin.

- The trace connecting between a decoupling capacitor to the associated via to the power/ground reference plane must be no longer than 200 mils and be 20 mils wide.

Of course, there are many more rules embedded in the experienced designer's head. A digital simulator may also pick up some of these rule violations, but software automation is not a surrogate for good design judgment, and doing forensics on your own designs.

Next, the examiner takes a look inside at the major organs – the PCB stackup and power distribution networks (PDN) in this case.

A poorly designed substrate, with inappropriately selected materials, can degrade the electrical performance of signal transmission, increasing emissions and crosstalk, and it can also make the product more susceptible to external noise. These issues can cause intermittent operation, due to timing glitches, and interference dramatically reducing the product's performance and long term reliability.

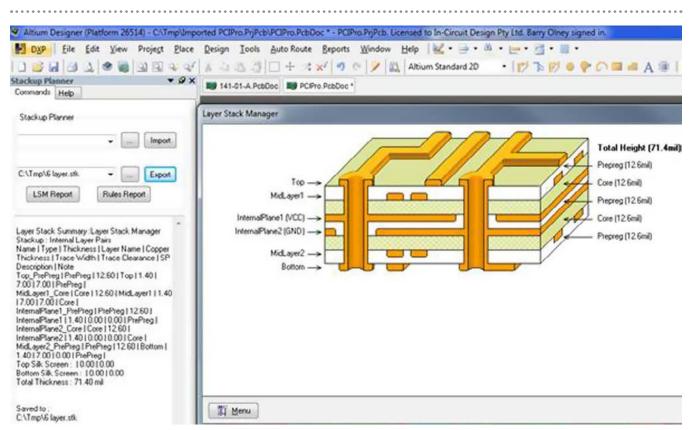

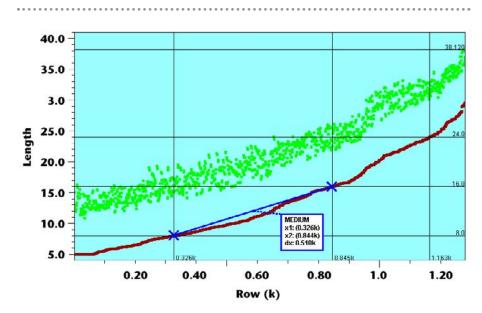

The less than desirable stackup in Figure 2 can be exported from Altium Designer (S09 to R13) into the ICD Stackup Planner to incorporate dielectric materials and adjust the stackup for optimal performance. The stackup is then modified to give 50 ohms single-ended and 100 ohms differential impedance by moving the plane layers and adding dielectric materials from the Stackup Planner's dielectric materials library.

Once modified, the stackup in Figure 3 can then be exported back to Altium Designer to also include impedance-controlled routing and differential rules. Plus, the stackup can also be exported to HyperLynx LineSim for pre-layout analysis, BoardSim for post-layout analysis, PADS and Allegro.

To promote communication with PCB fabricators, an Excel spreadsheet output (Figure 4)

Figure 2: Exporting the stackup from Altium Designer's layer stack manager.

is also available from the <u>ICD Stackup Planner</u>. It is for this reason that the ICD (.stk) format is fast becoming the industry standard for impedance controlled data collaboration between engineers, designers and fabricators.

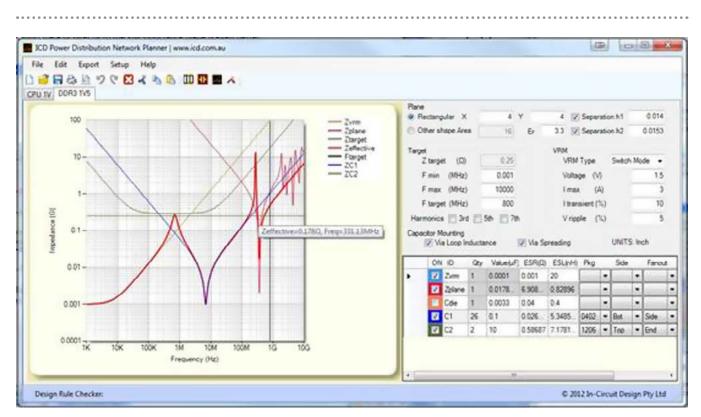

If the product is showing "flakiness" in functional tests, or even in production, the cause may involve inadequate PDN design. Ideally,

| ICD          | Steckup Plann              | er FX   Field Sal | iver Technology   www.icd.com.au                                  |                     |                         |      |                               |                |                     |                                  | 100                  |                                        |

|--------------|----------------------------|-------------------|-------------------------------------------------------------------|---------------------|-------------------------|------|-------------------------------|----------------|---------------------|----------------------------------|----------------------|----------------------------------------|

| File         | Edit Impo                  | t Export          | Setup Help                                                        |                     |                         |      |                               |                |                     |                                  |                      |                                        |

| 10           |                            |                   | × ○ @ @ @ ~ ∧                                                     |                     |                         |      |                               |                |                     |                                  |                      |                                        |

|              |                            |                   |                                                                   | (Class)             |                         |      |                               |                |                     |                                  |                      |                                        |

|              | Construction of the second | yer I a Layer I   | 10 Layer 12 Layer 14 Layer 15 Layer 18 Layer<br>ICD STACKUP PLANI | Cold an and see and |                         |      |                               |                |                     |                                  |                      |                                        |

| UNITS        | e mil                      |                   |                                                                   | 1/3/2013            |                         |      | Total Board Thickness: 62 mil |                |                     |                                  |                      |                                        |

|              |                            |                   | Differential Pairs >                                              |                     |                         |      |                               |                |                     |                                  |                      |                                        |

| Layer<br>No. | Description                | Layer Name        | Material Type                                                     |                     | Dielectric<br>Thickness |      | Trace<br>Clearance            | Trace<br>Width | Current<br>(Arride) | Characteristic<br>Impedance (Zo) |                      | Broadside Couple<br>Differential (Zdbs |

|              | Soldermask                 |                   | Dielectric                                                        | 33                  | 0.5                     |      |                               |                |                     |                                  |                      |                                        |

| 1            | Signal                     | Top               | Conductive                                                        |                     |                         | 1.40 | 8                             | - 4            | 0.31                | 52.93                            | 98.8                 |                                        |

|              | Prepreg                    |                   | (5 FR406 ; 2113 (1 MHz)                                           | 4.3                 | 2.9                     |      |                               |                |                     |                                  |                      |                                        |

| 2            | Plane.                     | GND               | Conductive                                                        |                     |                         | 1,40 |                               |                |                     |                                  |                      |                                        |

|              | Core                       |                   | IS FR406 ; 1080/2113 ; Rc+53% (2 GHz)                             | 3.89                | 6.0                     |      |                               |                |                     |                                  |                      |                                        |

| 3            | Signal                     | MidLayer3         | Conductive                                                        |                     |                         | 0.7  | 16                            | 8              | 0.31                | 54.14                            | 99.49                | 103.48                                 |

|              | Prepreg                    |                   | IS FR405 : 2116 (1 MHz)                                           | 4.3                 | 3.8                     |      |                               |                |                     |                                  |                      |                                        |

|              | Core                       |                   | IS FR406 ; 4-7628/2116 ; Ro=40% (2 OHz)                           | 4.3                 | 31.0                    |      |                               |                |                     |                                  |                      |                                        |

|              | Prepreg                    |                   | IS FR406 ; 2116 (1 MHz)                                           | 4.3                 | 3.8                     |      |                               |                |                     |                                  |                      |                                        |

| 4            | Signal                     | MidLayer4         | Conductive                                                        |                     |                         | 0.7  | 16                            | 8              | 0.31                | 54.14                            | 99.49                | 103.48                                 |

|              | Core                       |                   | IS FR406 ; 1080/2113 ; Ro+53% (2 GHz)                             | 3.89                | 6.0                     |      |                               |                |                     |                                  |                      |                                        |

| 5            | Plane                      | VCC               | Conductive                                                        |                     |                         | 1.40 |                               |                |                     |                                  |                      |                                        |

|              | Prepreg                    |                   | IS FR406 : 2113 (1 MHz)                                           | 4.3                 | 2.9                     |      |                               |                |                     |                                  |                      |                                        |

| 6            | Signal                     | Bottom            | Conductive                                                        | _                   |                         | 1,40 | 8                             | 4              | 0.31                | 52.92                            | 98.79                |                                        |

|              | Soldermask                 |                   | Dielectric                                                        | 3.3                 | 0.5                     |      |                               |                |                     |                                  |                      |                                        |

| Desi         | on Rule Check              | ec.               |                                                                   |                     |                         |      |                               |                |                     | © 2012                           | In-Circuit Design Pt | v Ltd                                  |

### Figure 3: The modified stackup can be exported from the ICD Stackup Planner back to Altium Designer.

| - |                | e - 10<br>6 8 1 11 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Nun D. Deuter                                               | 1 · · · ·                      | ¥8                     |                  | Superior and       | Red .           | inered in         | And an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Talantina (       |                                            |                                                    |         |