**FEBRUARY 2021**

# DESIGNOUS ENDER NO ENDER ENDER NO ENDER ENDER NO ENDER ENDER

## Master the art of keeping cool!

Learn how to beat the heat in your designs with techniques and methods from a fabricator's perspective.

Lively and insightful discussions from industry experts. Watch now!

App Notes and Fab Notes

Process Ionic Contamination Test (PICT) Standard

Achieving Operational Excellence in Electronics Manufacturing

Use of IMS Thermal Materials in Multilayer Stackups

## DESIGNO

## **Footprints and Library Management**

Many designers count footprints among their most common headaches. This is a critical point in the design process; errors at this stage can wind up having ramifications far downstream. Something as simple as an incorrect pad size can lead to bad solder joints or components floating during reflow. So, this month, we asked our expert contributors to share their thoughts on proper footprint creation and CAD library management.

### **FEATURES**

**Best Practices: Footprint** 12 **Design and CAD Library Management** Interview with John Watson

**FEATURES** 64

**Footprints:** A Distributor's **Perspective** Interview with Geof Lipman

**Footprint Design** 28 **Techniques: Don't Trust Datasheets** Interview with Tom Hausherr

**FEATURE COLUMNS Circuit Material Library** 68 **Considerations**

by John Coonrod

**Managing Footprints** 40 with Integrated **EDA Tools** by Matt Walsh

The Case for Expansive **72 Parts Libraries** by Bob Tise

**A Library Management 54 Cautionary Tale** by Stephen V. Chavez

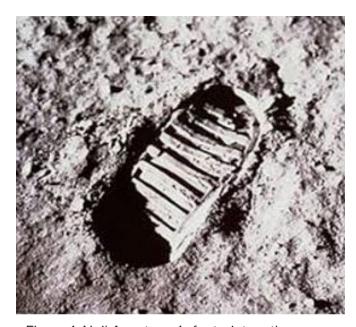

**Footprints— 76 Small Steps with** a Giant Impact by Kelly Dack

## DESIGNUU

#### **SHORTS**

- Shell, C3 Al, Baker Hughes, Microsoft 35 **Launch Open AI Energy Initiative**

- **How Unmanned Underwater Vehicles** 39 Could Become Easier to Detect

- Figure It Out: Closing the Gap Between 53 **College and Industry with PCEA**

- **Brain-to-Brain Communication** 63 **Demo Receives DARPA Funding**

- **Robot Race: The World's Top 10** 80 **Automated Countries**

### **DEPARTMENTS**

- 99 Career Opportunities

- 108 Educational Resource Center

- 109 Advertiser Index & Masthead

### **IPC APEX EXPO 2021 PREVIEW**

- Schedule at a Glance  $\Delta\Delta$ Full schedule of events at the show

- 46 Making the Most of a Virtual Event Interview with Alicia Balonek

#### COLUMNS

10 **Footprints and Library** Management by Andy Shaughnessy

22 **Developing Panel Level Semiconductor Packaging** by Vern Solberg

**Avoiding 'Blushing'** 36 and 'Bubbling' in Conformal Coatings by Phil Kinner

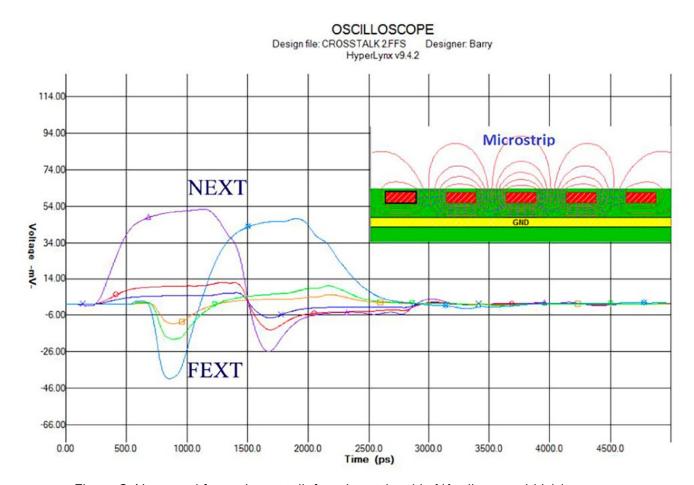

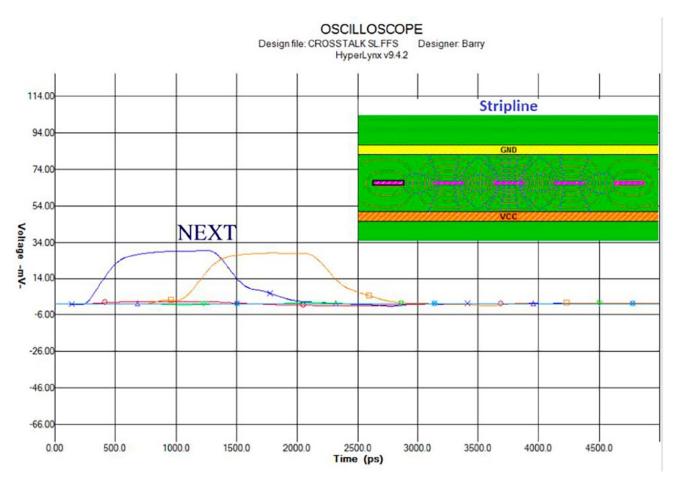

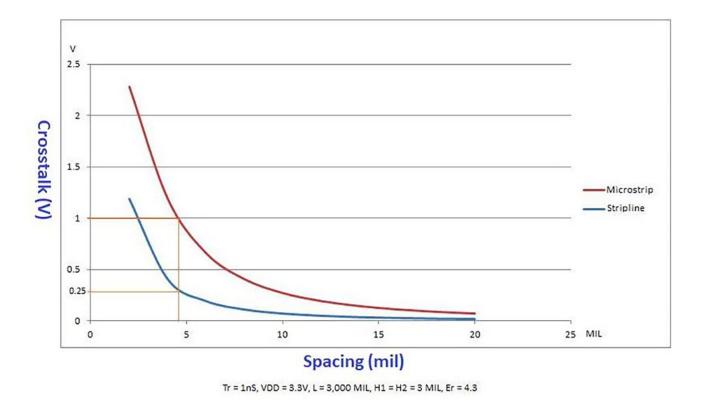

**Stackup Configurations** 58 to Mitigate Crosstalk by Barry Olney

#### HIGHLIGHTS

- 43 **PCB007**

- **71** MilAero007

- Top 10 PCBDesign007 96

##

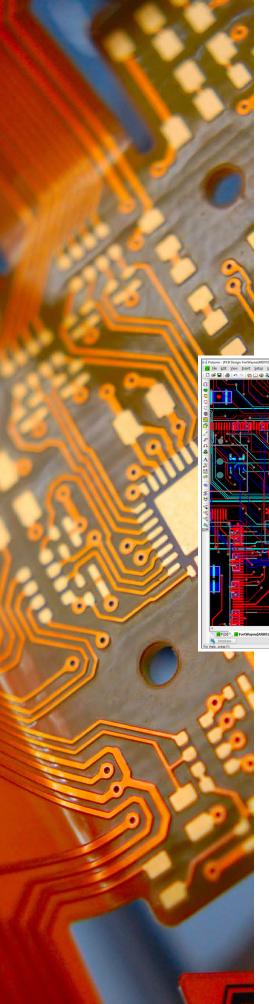

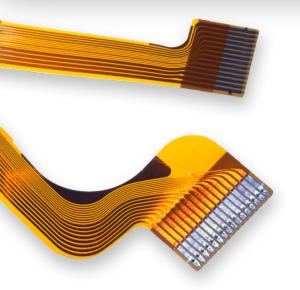

## **This Month in Flex**

Managing and creating footprints for rigid boards can be a complex task, but flexible and rigid-flex circuits offer their own set of distinct issues. If you're new to flex design, all of this can seem intimidating. This month, we break down the ins and outs of footprint design, and what it means to flex designers.

#### FLEXOO7 FEATURE COLUMN

IC Package Footprints: 82 Why So Many and How Many Is Enough? by Joe Fjelstad

#### **FLEXOO7 COLUMNS**

**PCB Technologies We Need** 90 **Now and Later** by John Talbot

#### **HIGHLIGHTS**

Flex007 88

#### **FLEXOO7 SHORTS**

Siemens, MaRS to Accelerate 94 **Innovation for Startups in Development of Autonomous, Connected Vehicles**

We offer an all-in-one solution through our experience, integrity, and clear communication. Get on board for the joint journey into the future:

## Footprints and Library Management

## The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

When we began planning this month's issue of *Design007 Magazine*, we looked at some of our recent surveys to get a feel

for some of your pain points.

These surveys are a great resource for us; they let us hear directly from the horse's mouth—in this case, the mouths of designers and design engineers.

In our last few surveys, many respondents mentioned footprints among their most common headaches. As always, the comments were illustrative. Here is a sample of the comments:

- Legacy issues with libraries, including traceability of footprints when used on PCBs across multiple projects over several years

- Wrong component footprints

- Incorrect footprint (smaller)

- Footprints are changed but not documented

- Errors on new footprints

- Incorrect footprints, as in just wrong (never been used previously, dimensionally incorrect)

I hear this sort of thing all the time from younger and veteran designers alike. As you

can see, these issues all begin in the CAD library. If you don't

have traceability for foot-

prints that are used on a variety of PCBs over the years, you have a serious problem. When your designers are changing footprints and not documenting the changes, you're just asking for trouble. Who's running your CAD library anyway?

The last comment on the list above is my favorite! You can tell by the "as in just wrong" snide remark that the respondent

is exasperated by the whole situation. It makes you wonder: Who signed off on these new footprints that were dimensionally incorrect? Does the company even have a signoff process? If so, does it include a quarantine for new footprints? It seems a little too easy for bad data to wander into this respondent's CAD library. It sounds like this company needs to install a Ring doorbell on their library so they can see who's coming and going.

In addition to bad or non-existent library management processes, there is another culprit: footprint creation itself. It's not a fun

task by any means, and it's not creative. Most designers and engineers don't want to spend their time creating PCB footprints, so the job often goes to a young designer or junior design engineer, and they can't wait to get out of the library and back to the real fun in schematics, layout, and simulation.

This is a critical point in the design process; errors at this stage can wind up having ramifications far downstream. Something as simple as an incorrect pad size can lead to bad solder joints or components floating during reflow.

So, mistakes are made, and many of these are "organic" mistakes created in-house, not imported in from a third party. But from an optimist's viewpoint, this just makes these mistakes easier to correct.

So, we asked our expert contributors to share their thoughts on proper footprint creation and CAD library management. First, we have an interview with Altium's John Watson, who shares a few horror stories to illustrate why the CAD librarian may be the most important person in your company. We also have an interview with Tom Hausherr of PCB Libraries, who explains sound library management processes and how to avoid many of the common hurdles along the way. Then, Matt Walsh of Siemens Digital Industries Software discusses the role of the EDA company in footprint creation and library management. We have an article by EPTAC's Kelly Dack that's full of tips and tricks for better library management. Stephen V. Chavez of Rockwell Collins discusses the need for proper, documented communication when utilizing your CAD library. Geof Lipman of Octoparts explains the type of data their customers are asking for, and offers advice for designers who are facing footprint challenges.

It's a busy time. We're getting ready to cover the virtual IPC APEX EXPO 2021, March 8-12. DesignCon has been pushed back to August 16–18 in the hopes that it can be an inperson show. I don't know about you, but I'd kill to go to a trade show!

See you next month. **DESIGNOO7**

Andy Shaughnessy is managing editor of Design007 Magazine. He has been covering PCB design for 20 years. He can be reached by clicking here.

## **Best Practices:** Footprint Design and CAD Library Management

### Feature Interview by the I-Connect007 **Editorial Team**

The I-Connect team spoke with Altium's John Watson about the hurdles surrounding footprints and footprint design. John talks about how being proactive and improving the CAD library can better QC processes and help protect against footprint difficulties.

**Andy Shaughnessy:** I'm here today with John Watson from Altium to discuss footprints, footprint design, and what can be done to achieve best practices. This came about because we recently conducted surveys asking for design problems. The results came mainly from designers, and around a quarter of them said footprint issues were a big problem.

**John Watson:** There's a real conflict in a lot of companies. They want to get their product to market. So, I think that the first issue that comes in with anything in a design is this conflict between the management schedule and the design schedule. If you're creating a new

component, for example, number one is that component needs to be put into quarantine. It's not used in new designs. It needs to be put into quarantine and checked. There's such a rush to say, "We've got to get this done and get it out." And there's just too much going on in a design to catch things that are wrong like that.

Barry Matties: How long should it be in quarantine?

**Watson:** It stays in quarantine until a couple of processes are completed. Number one, there is a QC process that's done on that component, and that QC process is actually multi-level. There will be different steps involved. For example, if you have a new component, you bring that component in or that footprint in, and you verify that footprint to the datasheet. On this first level of QC, you want to set up your verification documents to that footprint. What are we going to be looking at? We're going to be comparing this footprint to the datasheet, we're going to be looking at IPC standards, whatever the standards are that you're going to

## autolam: Base-Material Solutions for Automotive Electronics

Automotive electronics technologies are evolving at an increasing rate. Paying attention to the properties of materials at the substrate level is the first step towards achieving the most stringent performance targets of today's automotive manufacturers. autolam offers the solutions demanded by the diverse and unique requirements of automotive applications today and in the future.

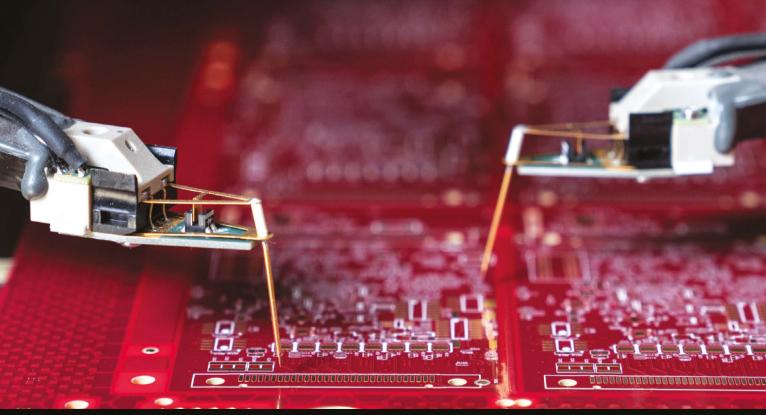

be lining this footprint up with. That's going to be your first level of QC, but I've actually seen where there's a second level of QC that's done. Once that part has been verified to the datasheet, that part then goes into what's called the prototype status; what it does is that component is then put onto a PCB, kind of a live test.

When that board comes back with the component on it, you look at it under the scope to see if there are any issues with the soldering. It's like a real-world environment. Those are the two levels of QC. Number one, you compare it to the documentation, and then you have a real-world environment that you take it through. That step and those processes are what you go through. That way, you've actually had both sides of it: You have your side of it, and then also the assembler's side of it. I've found that a lot of times, believe it or not-I know it's a shocking comment I'm about to make—but datasheets have been known to be wrong. VPs have no understanding of what it takes to put a PCB design out—the steps, the checks that you have to do, all these different things. Often, that's lost in this whole process.

**Matties:** You mentioned time is a critical factor, but what about communication?

**Watson:** That's huge. Especially on the communication. Cool Hand Luke had it right in the movie: What we have here is a failure to communicate.

**Dan Feinberg:** John, along with what you were just saying, so many customers are saying the footprint is so wrong. I mean, they're emphasizing that. Do designers not realize that the footprints are so wrong or deemed to be so wrong? What's happening with the communication that they should be so surprised that it's wrong?

**Watson:** I would totally agree with that. There is a huge lack of communication. Especially with what I've seen for the past year, with

John Watson

everything that's been going on. Teams have been put into a lean mode, where you don't have as many people working on projects anymore. The very first rule of QC is not to check your own work. You never QC your own work. You always have another set of eyes look at it and then line it up with the verification documents. Too often now, that is being skipped over.

With that said, another issue that comes up a lot is that minimal pieces of that footprint are put in. If you took a footprint of a component, it's a cookie cutter; each footprint should have exactly the same thing in it. There should be the copper, solder paste, and the solder mask. There should then be the placement courtyard for that component, and there should be assembly information in that footprint. But because of time and manpower issues, shortcuts are taken, and every time you take a shortcut in a PCB design, it's absolutely adding risk to that design. It's something you just can't play around with when it comes to the PCB design.

When I joined Legrand, an engineer pulled me aside to his desk, and opened a drawer halffull of FR-4 boards. He said, "Those were our

failures." I was shocked, but once I learned more details, I found that over 30% of the boards were failing to get through fabrication because of problems with footprints or things like that. Now, we go back to cause and effect. "Okay, what's the cause?" It was our multiple libraries.

As a matter of fact, we had 1,123 libraries that we were working from in Legrand, and you cannot manage that many libraries. You just can't do it. You must have a singular library that can be managed. One Friday evening, after everybody went home, I deleted every single one of their libraries and their backups, and I purposely came in late on Monday morning. I knew what was about to go down.

As soon as I walked in, the whispers began: "He's here." Everybody was in the conference room, and I said, "As you probably have now realized, all your libraries are gone. We're starting over, and we're starting with a singular library which we can manage and control." I knew it was the only way you could fix the effect. The effect was bad boards, and we had to go back to the root cause.

Matties: One thing you did was to require everybody to stop doing their busy work and take that time. They're under time pressure, and a lot of companies may not be willing to take that time, I would think.

**Watson:** Yes, you've got to look at the whole picture, though. "Okay, we're losing time redesigning a board."

**Matties:** People don't stop to delete thousands of libraries because the thinking is they don't have the time to do it.

**Watson:** Exactly. Why is it that we have time to do something again, but we don't have the time to do it right the first time? We kind of compartmentalize our processes and we don't look at the big picture. We always talk about saving money. How much money was wasted

in an engineering drawer of boards that were just wasted?

The other comment I wanted to make about libraries and footprints is you've got to have a single library, period, because that's what's managed and what's controlled. Now, there are changes that happen all the time on libraries. IPC, for example, just came out with 7351C. There were some real major changes they did with footprints from revision B. That's where they brought in rounding off the pads and different things like that. How do you make those changes in your library when you've got 1,000 libraries?

**Shaughnessy:** Nobody likes dealing with that stuff. How did they get to that point? How would you know where to look and which library to look in? I mean, I guess that's a whole other string of nomenclature or whatever. What a nightmare.

**Watson:** It was actually a living nightmare. Usually, every design that went through had its own library, and every designer had their own library, what they liked, what they preferred, and what their standards of a component were. I've been doing design for 20 years. When we first began, we used to take a resistor that consisted of a symbol and a footprint. We would lay down 0603 resistors of a certain value, we would just copy that same resistor, lay it down, change the value—just copy and paste. That's the way we did our schematics. Now, components have so much in them, which is phenomenal. This is really nice.

When you have a component, what are we looking at? We're looking at the symbol and at the footprint, but now we're also adding in parametric information in that component. Now we have sourcing, we have the manufacturers who will build that component for you who will be your vendors, who will sell it to you. Now we've even tied in component dynamic information: What are your vendors' quantities right now and what is their pricing?

What are their price breaks for that component? It's all inside that component now. It's not the old days anymore.

There's another great point I would like to make. There needs to be a signing off the footprint, and of the process. It's amazing that people's memory doesn't last more than six months when it comes to the mistakes that they make. They say, "I didn't approve that." But I reply, "Okay, well, there's your signature." And some of the solutions involved are going to be, first, biting a really difficult bullet for some peo-

ple. That's because it needs changing, and people don't want to change.

**Matties:** When you talk about the root cause, how are they going to identify the root cause? What process would you use?

**Watson:** I would go through the five whys. That's how I get to the root cause of an issue. You look at the problem and ask why it happened. Then you go back one step, and ask why that happened? Let

me give you an example. If my battery was dead in my car, my first question is, why is my battery dead? The answer to that question is my alternator was not charging my battery. Okay, why wasn't my alternator charging my battery? Because of a loose belt on the alternator. But why was there a loose belt on the alternator? Well, because I haven't replaced it for five years. So why haven't you replaced it for five years?

You keep walking back through the problem like that and you go back five whys and you start getting into the root cause. I go back to the fifth reason and find out I don't follow the maintenance schedule on my vehicle. So that's where you begin. There are different systems like that. And fishbone charts can help you figure out what your root causes are.

**Matties:** When you talk about market changes, how do they affect footprints?

**Watson:** The only effects of the market on the footprint would probably be big swings. I know when we went to solderless, the solderless manufacturing had a big impact on footprints and solderability. We saw how the market trending affected how the footprint was, but these are going to be common changes; maybe not common, but these will be changes in the market, and there will be changes that happen in

> footprints. Like I mentioned about IPC, they suggested, "Okay, now let's round off your corners." So, they put out the general direction to improve the footprint. IPC is really strong on that side of it, to watch what is affecting the footprint.

> The other thing is just that the effect is more how those components are controlled and managed. How do you handle these changes? There are always going to be changes, so how you handle those changes is what's

more important. How do you implement the changes? How do you go ahead and make a change on a footprint, for example? It goes back into the QC process. Make sure that the change was correct, and that it's done right. Then you take it back into the prototype stage, put a real component on that part, put it under a microscope, look at the solder joints and things like that, and understand what looks good; that's the way it should be.

**Matties:** What's a typical timeline for that process? Is that a day or a couple of weeks?

**Watson:** No, it could be within a day. It's very easy. It's a very good process.

## Paying Attention To Details Achieves Excellence.

Superior Advanced Technology Capability World-Class Engineering Support A Diversified Offshore Supply Chain

> **APCT HAS THE SOLUTIONS** 512.548.7435 | APCT.com

Circuit **Board Solutions** Printed

**Matties:** What I'm looking at is keeping this QC and this quarantine process in mind, balanced with the time pressure.

**Watson:** That's true. You have to take the steps to be proactive in this process. You can't be reactive. That's probably what is really key; you have to not assume that that component is correct. You assume it's not correct until you prove differently, and that's probably the motto that should be plastered onto anybody who even touches a component. It is wrong until you prove it otherwise.

**Nolan Johnson:** John, that raises a good point as far as where these footprints are coming from in the first place. You have to assume it's wrong until you prove them right. So where do they come from in the first place?

**Watson:** Probably one of the biggest mistakes I've seen in companies is that they give edit rights or permission to everybody to create libraries or create a component. They think it's more efficient for them to let everybody create components. This was actually a policy I saw done in a company when we were setting up their libraries and getting this started for them. I said, "So who's going to

be your librarian?" They said, "Oh, no, we're not going to have a librarian. Everybody's going to be able to create components." I said, "I would suggest not to. That's not going to work." Their reply was, "No, no, no. It's going to work for us." I'm not the sort of person who goes nose to nose with you to prove to you what you're doing is wrong. So I said, "Let's go ahead and let's run this policy to see how it goes." I just began putting footprints and components up on the screen, and I said, "What do you see wrong here?" I mean, there would be stuff that was just so blatant, like rotated pads, everything.

That just brings up the complete process. First off, who's touching these components? Who has the permission? I would say that you give one individual or maybe a couple individuals that right. I label the librarian as the most important person on my team.

**Johnson:** One of the things that I'm hearing here is there's a lot of design team attention and effort being put into parts, components and footprints; into managing and verifying those, and making sure they're accurate. And yet, at the same time, if a CAD tool is like a word processor, the mark definitions are like fonts. Why do we have individual design teams out there building all their own fonts?

**Watson:** That's a really good point and a really good question. I don't understand exactly why they would do that, to be honest.

**Shaughnessy:** Would it be because they can't trust the datasheets? If you're assuming it's wrong, do you build a better mousetrap? Or do you work with what they gave you?

Watson: Yes, exactly. It's why I've actually seen libraries, when you go in there, they're like, "We're going to have an 0402 resistor, and we're going to put in all 32 heights of that resistor because we want to be precise." It's a lot less impact on the footprint of a component because you're going to perfect that 0402 resistor footprint, for example, and then you're just going to repeat that. You're just going to reuse that footprint.

You're going to start seeing that get cleaned up and then it just goes from there.

Johnson: John, on average in a new design, how much of the design time do you think typically is devoted to making footprints, verifying footprints, and getting that in order of the overall design?

**Watson:** I would say, number one, it's once you establish the sound processes of the process flow from the time that a component is needed to the time it's QC'd. I will say the initial QC, when it goes on a board, is probably about only about 10-15% of the process. Because what can happen is you then start cookie cutting. A component is going to have the same exact pieces to it, and then you can start cookie cutting it and then it's very minimal. I mean, if you have a very established process, it's very secure and also very low risk.

**Johnson:** Right. That makes sense; if you can get it to a well-defined process that is probably down to the 10-15% range. If you don't have good processing, you're probably up in the 30% range.

**Watson:** Exactly. And then you're going to see other effects of having bad components also. You know, when you have 30%, when you have no process, the chaos begins. I've used this analogy before but imagine if the mayor or government official would come forward and say, "Okay, no more rules. No one's going to be arrested for anything. You're on your own." What is the result of saying we have no processes, no rules, nothing? The result is chaos. That's what happens. There has to be the rules and the processes. Right now, I'm working with a couple of companies regarding their libraries and establishing their processes on a consulting basis, and I can tell you that one of them said, "We really don't know what we're doing." Okay, good. That's a good position to be in.

Matties: You've got to start with the truth, right?

**Watson:** Exactly. I told them that it's a great position to be in because now you're like clay; you just mold yourself into the processes that you want and put those processes in place and make sure that your components are correct and everything else. It has hit all of us at some point when I think about it. It's a nerve-wracking feeling when you've put out a PCB design, and you haven't checked footprints. You wait for that phone call from the assembly house to tell you, "Oh, by the way, we can't put your component on your board." And then you have to make the long walk into your manager's office to explain to them why you just wasted tens of thousands of dollars on a board that is now wasted and you're just going to turn them into coffee cup coasters.

## It's a nerve-wracking feeling when you've put out a PCB design, and you haven't checked footprints.

You're actually talking about increasing the value of your team. When you become more efficient and run more efficiently, it's not just adding another PCB design to your team, it's also adding another team member, for example, or the value of a team member to the team. Because now you're running much more efficiently.

**Matties:** And the thing about  $X = X_C - 1$  is you get to identify what your X is, and what we're saying is it doesn't have to be a grand slam because continuous improvement is an incremental endeavor. Reduce your spins by one, reduce your design time by a day, reduce your

rotation, etc. Really, to use  $X = X_C - 1$ , you have to incorporate your five whys.

**Watson:** Exactly. You have to get back to the root cause. What is not working? I mean, you've got to look at the backend. But there's another process here also, once you've taken a component through creating it, first defining who's going to do it, creating the process, taking it into quarantine, QCing that process, and getting it into prototype. Yes, it looks good from there. The one thing I've actually written about is that there's never a finish line in the library. It's not like you look at your library and say, "We're all done." There's always going to be that tailoring process at the very end where you now get more information from people. Everything filters back. It's one big circle.

**Matties:** In your experience, John, do you find the 80/20 rule to be true? That 80% of the issues come from the library?

**Watson:** Yes, exactly. A lot of the issues that occur on the library are filtered back to the library. A lot of times when you have a library that you've been working with for a while you stop the tailoring process. You never look at your footprints and ask how you can improve this footprint. It's always going to be improved on. You're always going to say, "Yes, this can be improved on here by doing this or that." Maybe there are now recommendations coming in

from IPC. There's always that polishing of that component. It's a complete process here; it's not straight or linear, it's circular.

**Matties:** How many points of data or information would one component have in the library? Is that user defined, or is there a standard that you would follow?

**Watson:** It could vary. When you're talking about parametric information on a component, that could be endless, actually. What will happen is you begin to categorize components into what would be categories and families. If you go into Digi-Key and pull up a component, it will show you this is your category, and this is your family of components. Those families of components will start having a generalized parameter of information. The families will have general parameters of information attached to each family. And that's kind of the way you would organize your library also.

There are two things about a library. Number one is you want to be able to find things quickly and find them accurately, and then number two is you want to structure your library in a way where it rolls with the company. A library is not a static item. It's a very, very dynamic item. It has to grow with your company.

**Matties:** Do you think that if a process is followed as you're describing, you'll never miss a footprint?

**Watson:** If you do, I would go back to the five whys.

**Matties:** But the odds of missing it have to be reduced.

**Watson:** Yes, it has now decreased considerably. What you're pulling out of this is that your "minus one" is risk. You're pulling risk out. You're not just creating a component and throwing it against the wall and hoping it sticks. That's the real concern with that. The other thing is that with some of the comments I've heard about components, for example, we get replies from people and they say, "It's close enough, the component, the model. It's pretty good." But is it correct?

Just because you're able to put a component in a spot on the board does not mean the footprint was correct. That just means you got lucky. There are situations where footprints have been wrong and after a time those problems show up. Let's say you had a wrong pad size that caused a short or less solder. After a time, now you're seeing problems introduced and issues that come up with that footprint. But a lot of times, the mentality is, "We got it. We made it."

**Matties:** But it's still a science and not an art, correct?

**Watson:** I would think so, yes.

**Matties:** Again, if you follow the process.

**Watson:** If you follow the process, yes.

**Happy Holden:** I was involved in design with a company that had been doing it for 50 or 60 years like I was, and nobody was a librarian out of 300 or 400 PC designers, and that's because they learned the hard way that components are so important and that components have a life. It was better to have corporate engineering create all the libraries worldwide, includ-

ing the expensive models and things like that, but also to be tied in very tightly with corporate quality and field service. Once a component was approved, and the model and the footprint were generated, it was tied to the purchase of that part and put away in a catalog so that design engineers could select from the catalog, and specifically in that catalog was the cost and the field service quality. Bad parts that were coming back from the field, not due to manufacturing errors, but the component itself were highlighted in those lists to stay away from these "known bad actors."

Watson: Right. As I said, the librarian is the most important person on my team.

**Matties:** John, this has been a very informative conversation. Any final thoughts to this conversation?

Watson: I would say that whenever there's a problem or issue like wrong footprints, you're going to have to take a step back, take a deep breath, look at it in a more objective way and ask yourself this one question: What went wrong and why? What happened here? Why did it happen? Be honest with yourself. I mean, people should be able to say, "Yes, the buck stops with me. I made a mistake." And then deal with those mistakes and issues and move forward.

And watch out with connectors. Your biggest problem will be with connectors, because the datasheet does not tell you how the pin numberings are, whether they are one down the row or they're alternating, and that actually will cause major problems when you get into fabrication.

**Shaughnessy:** This was really good. Thanks, John.

Watson: Guys, thank you very much. DESIGNOO7

## **Developing Panel Level Semiconductor Packaging**

**Designers Notebook** by Vern Solberg, CONSULTANT

Semiconductor packaging has traditionally utilized a narrow strip of organic copper-clad organic-based laminate and wire-bond processing for the single-die BGA. Companies furnishing devices for high-volume markets are now implementing very fine-pitch alloy bumped flip-chip package technologies that enable face-down interface. The terminal size and pitch are often, however, far too small for conventional organic circuit board fabrication capability. To better accommodate die-tosubstrate interface, several companies are successfully adopting wafer-level and panel-level package technologies.

### **Wafer Level Packaging**

Silicon materials are commonly furnished in a 200-300 mm diameter wafer format sized to be compliant with the existing semiconductor fabrication infrastructure. Most commercial semiconductor manufacturers utilize these thin silicon wafers to provide a stable base for integrated circuit processing, but the silicon-based material has also proven to be an excellent choice for wafer-level packaging because it perfectly matches the CTE of the silicon die element(s) that will be mounted onto its surface.

Fabrication of the fan-out or fan-in/fan-out interposer is commonly performed within the semiconductor foundry environment. Die elements are arranged on the wafer's surface in a row and column format, with the active surface facing up for wire-bond interconnect or face-down when furnished with alloy bump terminals.

The processes for via-hole ablation and metallization in the silicon material are very different from the basic semiconductor man-

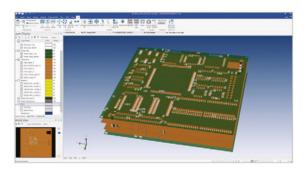

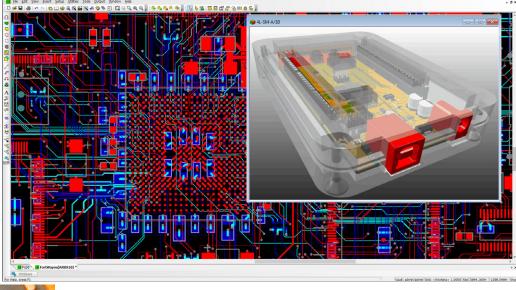

Integrated Tools to Process PCB Designs

**Document**

Quickly and easily specify the PCBs form, fit and function.

Use manufacturing data to generate a 3D facsimile of the finished product.

Ensure that manufacturing data is accurate for PCB construciton.

Minimize costs in both PCB fabrication and assembly through maxiumum panel usage.

**Panelize**

**CAM350**

Verify and Optimize PCB Designs for Successful Manufacturing

Drive Fabrication, Assembly & Inspection

DownStream Technologies, offers an integrated manufacturing data preparation solution for PCB post processing including manufacturing data visualization, stack-up definition, PCB panel visualization and support for 3D PCB documentation. This environment allows PCB designers and engineers to visualize, verify and document a printed circuit board before manufacturing.

800-535-3226 downstreamtech.com

©2019 DownStream Technologies, Inc. All rights reserved.

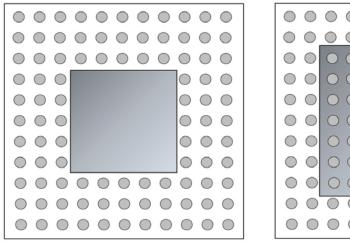

Fan Out WLP

Fan-in / Fan Out WLP

Figure 1: Comparing the fan-out to the fan-in/fan-out wafer-level package.

ufacturing processes. Metal deposition processes developed for the silicon-based interposer enable the redistribution of the very closely spaced terminals on the die element's perimeter to a uniform and wider spaced array pattern that will enable a more efficient package substrate interface (Figure 1).

Although the silicon wafer packaging process has proven robust and reliable, the cost associated with silicon-based interposer fabrication has been a primary detractor, and because the wafers are round, there is a great deal of surface area at the wafer perimeter that cannot be populated. In the effort to trim overall packaging expense several alternative panel-level packaging methodologies have emerged.

### Panel Level Packaging

Both independently and through consortia of academia and industry, several viable solutions have evolved that provide the same fanout and fan-in/fan-out interface capability. Panel-level packaging will continue to use silicon as a base, but alternative lower cost organic epoxy-glass laminate and panel formatted glass are viable options.

### Silicon and Glass Panel Development

To gain better utilization of the silicon base,

some companies have moved away from the traditional wafer level format to a square silicon or glass panel format where the individual die elements can be arranged in the same row and column format with minimal base material waste.

## Silicon Interposer Base Material

To maximize assembly efficiency the base material can be furnished as 300 mm and 500 mm square panels, but some companies looking to maximize package assembly efficiencies are fabricating panels as large as 600 mm square.

Silicon-based interposer fabrication requires a rather specialized and complex sequence of processes that begin with via-hole formation. Although laser ablation can be adopted for forming the micro-via holes, the process most commonly employed for volume applications uses a deep reactive-ion etching (DRIE) process (often referred to as the "Bosch" process). This methodology can provide very small hole diameters that range between 5-20 microns. In preparation for conductor forming and via filling, a seed layer of copper or tungsten is applied to enable electroplating the additional copper required to complete the via-fill operation. Further pattern imaging and plating processes are engaged to provide interconnect features on the outer surfaces of the silicon substrate.

## Glass Interposer Base Material

Significantly less costly than silicon, glass panels are being supplied by several companies specializing in manufacturing a physically durable glass with properties suitable for fan-out and/or fan-in package applications. The nominal CTE of the metalized glass panel is also a very close match to the silicon die  $(3 \text{ ppm/}^{\circ}\text{C}).$

Glass is available in panel thicknesses that range from 50  $\mu$ m to  $\geq$ 700  $\mu$ m, and the process differs significantly from silicon wafers because it will not require back grinding and polishing prior to via ablation and plating operations. The via-hole forming processes for glass include laser and electrostatic discharge as well as mechanical drilling using micro-sandblasting. Metallization on glass begins with a vapor deposition (PVD) process of copper or silver ink deposition to furnish the base for filling vias and interconnect circuitry.

## High Tq, Low CTE Organic Base Material

One of the more promising materials for the high-density organic package substrate applications is promoted as an ultra-low CTE organic glass reinforced bismaleimide triazine (BT) based laminate.

While many organic dielectric materials have traditionally proven suitable for a broad range of wire-bond package applications, several leading suppliers have developed a more advanced laminate material that closely matches the very low thermal coefficient of expansion (CTE) of the silicon die element, as well as meeting the fine-line interconnect challenge for new generations of high I/O face-down mounted semiconductors. The manufacturer promises that the laminate will provide a more stable platform for mounting silicon-based semiconductor elements.

The design guidelines furnished in Table 1 relate to copper alloy via filling and conductor formation for the three base material candidates for panel-level semiconductor packaging. The geometries furnished were developed from research by the author and consensus

| Attribute       | Silicon           | Glass             | CTE Matching      |

|-----------------|-------------------|-------------------|-------------------|

|                 | Base Material     | Base Material     | Organic Material  |

| Substrate Panel | 200μm to 3mm      | 200µm to 3mm      | 100 to 800µm      |

| Thickness       | (~.008" to .120") | (~.008" to .120") | (~.004" to .032") |

| μVia Hole       | 5μm to 20μm       | 10μm to 30μm      | 10μm min.         |

| Diameter        | (~0002 to.0008")  | (~.0004 to.0012") | (~.0004")         |

| μVia Land       | 15 to 25µm        | 25 to 50µm        | 20µm min.         |

| Diameter        | (~.0006 to .001") | (~.001 to .002")  | (~.0008")         |

| μVia Hole       | 30 to 50µm        | 50 to 100µm       | 40μm min.         |

| Pitch           | (~.0012 to .002") | (~.002 to .004")  | (~.0016")         |

| Base Core       | 2µm min.          | 1μm to 5μm        | 3μm min.          |

| Line/Spaces     | (~ .00008")       | (~ .000040002")   | (~ .00012")       |

| Build-up        | 2µm min.          | 1μm to 5μm        | 3μm min.          |

| Lines/Spaces    | (~ .00008")       | (~ .000040002")   | (~ .00012")       |

Table 1: Panel-level package design guide.

among several colleagues involved in the technology.

The data shown may not reflect the capability of all suppliers in their respective categories, but supplier companies will generally furnish the designer with alternative design guidance related to their material sets and specific process capabilities. The supplier-developed interposer design guidelines will generally reflect factors derived from their experience, ensuring that they will likely furnish a reliable product with a high degree of quality and process yield.

## **Key Planning Issues for Panel Level Packaging**

Assembly process methodologies will vary a great deal. Issues that will need to be resolved prior to beginning the development process include:

- Availability of semiconductors prepared for face-down mounting

- Establishing reliable sources for semiconductor elements

- Specifying physical and environmental operating conditions

- Defining package design constraints and process protocols

- Stipulating electrical test method and post assembly inspection criteria

Semiconductor packaging methodology will continue to evolve, and market analysts project a steady growth in semiconductor package applications.

There is presently a global effort by members of SEMI (Semiconductor Equipment and Materials International) to develop standards for manufacturing panel-level packaging. The standards have already established panel size variations and thickness, as well as surface topography and panel warpage limitations.

IPC is currently in the formation stage to develop a standard guidance document for an organic-based panel format that is defined as "a wiring structure produced with a printed circuit board fabrication process that provides the final electrical interface between microelectronic devices and the underlying circuit structure." Printed circuit manufacturing process characteristics include the use of square or rectangular panels with build-up circuit layers applied to both sides of the base using organic dielectric materials. DESIGNOO7

Vern Solberg is an independent technical consultant specializing in SMT and microelectronics design and manufacturing technology. To read past columns or contact Solberg, click here.

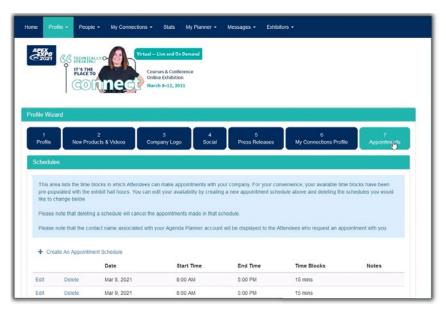

Courses & Conference Online Exhibition March 8-12, 2021

Register for our virtual event at **IPCAPEXEXPO.ORG**

## Footprint Design Techniques: Don't Trust Datasheets

## Feature Interview by the I-Connect007 Editorial Team

The I-Connect007 Editorial Team recently spoke with PCB Libraries CEO Tom Hausherr, who has spent much of his professional life dialing in the processes related to footprints and CAD libraries. We asked him to run down some of the more common challenges that he sees, as well as some solutions and workarounds. One point emerged several times during our chat: Don't trust datasheets.

**Andy Shaughnessy:** Tom, our readers tell us in surveys that footprints are a huge problem for them, and a lot of it seems to come from bad CAD library management. What are some of the more common challenges you see with footprints?

**Tom Hausherr:** The number one mistake today is the polarity marking on diodes, where the EE engineer puts Pin 1 on the cathode and puts Pin 2 on the anode. Then the designer does the opposite. They populate the boards and when they plug them in, something smokes or doesn't work properly.

**Barry Matties:** That is a pretty common problem that we hear about. Why isn't more care given to that if it's such a common problem, Tom?

Hausherr: I try to label the pins of the diode C and A on both the schematic symbol and PCB footprint so that you cannot possibly get it wrong—C for cathode, A for anode. But then again, when you're dealing with LEDs, many manufacturers put the polarity on the anode side of the component package. Electrically, the anode is the positive pin, and the cathode is the negative pin. But the marking indicator is on the cathode for diodes. To eliminate error rate, double check all diode and LED connections.

**Matties:** Right. We hear the same, not just with the LEDs, but with connectors, too, being a big issue with pin orientation.

**Hausherr:** A lot of the connector manufacturers do not provide any pin assignments on their datasheets. I run into this all the time. You should coordinate connector pin assignments with the EE engineer's schematic. Also,

While others struggle just to keep pace, we stay ahead of the curve by constantly investing in the equipment, people and resources needed to be the best total PCB solutions provider in the industry.

**VIEW OUR CAPABILITIES**

Tom Hausherr

some of the connector manufacturers give you the location of Pin 1 but not Pin 2. I wish all component manufacturers knew what information to provide in their datasheets to make our job easier.

The number one feature that's missing in most component datasheets is the manufacturer-recommended footprint pattern almost never provides dimensional data from the hole or surface mount pattern to the edge of the connector body. This is a necessary piece of missing information that causes errors. This can be checked when the 3D model is inserted into the footprint pattern to ensure the silkscreen and assembly outline matches the package boundary.

Another thing about the connectors: You must use their manufacturer-recommended pattern. There's no IPC calculator or magic formula for calculating a complex connector pattern. Many of the connectors today are a mixture of plated-through mounting holes and slots, non-plated alignment holes, surface mount pads, and every type of combination. So, you must use the manufacturer pattern.

I just did a library part last week, a 15-pin D-Sub miniature connector. We built it per the manufacturer pattern and exactly per their dimensions, but there was a datasheet typo. The only thing that saved us from duplicating the error in the datasheet was the 3D model. The mounting holes lined up with the 3D model, but all the pins were in the wrong location.

I looked at it, measured everything, and everything was correct by the datasheet. And then I found out that the manufacturer had one dimension wrong. They dimensioned the mounting hole to Pin 1 but the value was to Pin 5. In other words, there was an inherent typographical error in the manufacturer's datasheet. So that's another thing to be very careful about. Double check with the 3D model.

**Shaughnessy:** Datasheets have errors after all.

**Hausherr:** Right! Hard to believe. Let me give you an example. I did a design a couple of years ago with a large 200-pin LGA. I sent the design Gerber data to a fabricator. Before they built the boards, they ran a Valor VPL check. And there was nothing wrong with the pad sizes or the land pattern, but they did catch an error in the pin assignment. The component manufacturer did not indicate "top or bottom" view, so I guessed. The alphanumeric pin assignments were all incorrect.

When they ran the Valor VPL check they discovered that all the pin numbers were backward. Now, let's say that they didn't run the Valor VPL check. They would have manufactured and assembled the boards, and everything would have assembled perfectly. But when the EE engineer turned on power, none of the PCB functions would have worked.

In my case, all the terminal leads were fine, but it was the pin assignment that was totally backward. The Valor VPL check caught that mistake. Unfortunately, I had to redesign the board at my expense. But that one little catch saved thousands of dollars in fabrication, assembly, and components. The board would have been declared a door stop.

**Shaughnessy:** What is the cause of that in the first place?

**Hausherr:** When the manufacturer's datasheet shows the top view and the bottom view, they must clearly define which is the top view and which is the bottom view, and what you are looking at. Often, they mark the pin assignments, and some manufacturers are kind of lax at labeling all this documentation. Also, the LGA package pin assignments are sometimes intentionally mirrored.

Nowadays, the component manufacturers are giving acceptable recommended footprint land patterns. They call them the "Recommended Footprint Pattern," just the "Recommended Pattern," or "Solder Pattern." PCB designers or CAD managers are split in two. I would say that half of the global PCB industry prefers the manufacturer pattern, the other half of the industry prefers to use the IPC calculator pattern, and there are some who use a combination of both. But land pattern calculators are software code that are not flexible enough for non-standard packages. As we move to the future, standard packages are being replaced with complex nonstandard packages to intentionally eliminate competitors from producing lower cost alternatives. These new non-standard packages require manufacturer-recommended patterns.

We have 100,000 users of our software program worldwide and we run into this every day. We add the manufacturer-recommended pattern data in all our CAD library data files, but those can be turned off and revert to the IPC pattern. We have several millions of manufacturer part numbers on our cloud database. For instance, Boeing would download a bunch of parts and then say, "Why do you put the manufacturer's pattern in here?" I said, "Well, it's easier for us to do that because all you have to do is uncheck a box and then it defaults to the IPC pattern." And they said, "Yeah, but we downloaded the whole bill of material with the parts and now we've got to go and uncheck all these boxes and resave every part to get the IPC pattern."

It's really hard to please everybody. You go after the manufacturer's pattern, and a lot of times the manufacturer's pattern is superior to the IPC specifications. I've downloaded millions of datasheets and checked everything out, checking against both different mathematical models and the manufacturer's recommendation. Then, it's knowing which pattern is best after looking at millions of land patterns and millions of footprints. However, we've been creating land pattern calculators for 20 years and no one has ever complained about creating a bad footprint.

Alternatively, we've never heard of anyone complaining about using a manufacturer's recommended pattern, as long as the terminal leads are on the pad. I'm sure that there are typos in datasheets, so the PCB designer must ensure that the terminal lead is on the pad and our software calculators clearly indicate both the terminal lead location in respect to the pad location.

And it's difficult. If you have a QFN bottom terminal component with a thermal tab, some manufacturers provide recommended stencil data pattern. You have to know stencil data pattern rules. You've got to have a 0.20 mm "minimum" web between these patterns and stay within 0.10 mm from the pad edge. And if the calculator calculates anything less than that, you're going to get a small web in between the stencil apertures. When they go to assemble it, they're going to use that stencil a dozen times and shred it because the web between the apertures is so small. But the stencil manufacturers should know this. And they should make the stencil a bit more rugged for the paste mask application process.

Shaughnessy: Tom, Happy mentioned a few weeks ago that the standards in some countries and some of the manufacturers' own numbers were far superior to IPC's standards.

Happy Holden: Yes, JPCA had been using leadfree solders for a lot longer than we had. And because of their focus on miniaturization and the fact that lead-free solder was much stronger than tin-lead solders, their land patterns were much, much smaller than ours.

Matties: So, Tom, when you are perhaps instructing a class or educating your customers, what would you tell your students regarding footprints and how to avoid a failure?

**Hausherr:** If I were going to do a class, I would say that accurate 3D models would have to be mandatory for quality control. I went to work for a company in Orange County, California, five years ago and I worked side by side with

## If I were going to do a class, I would say that accurate 3D models would have to be mandatory for quality control.

a gentleman who knew SolidWorks inside out. He did everything backward: He took the package dimensions and meticulously drew the 3D component model in SolidWorks, then took that model and designed a pad pattern underneath it. He created his own toe, heel, and side solder joints from the 3D model. It was kind of like reverse engineering. You create the 3D model first and then you create the solder pattern after the 3D model.

**Matties:** If you follow that strategy, whether you do it first or second, the modeling shouldn't have any errors related to footprint mismatch.

**Hausherr:** Yes, the 3D modeling must have the highest integrity. The model must be created using the exact package and terminal lead dimensions. When you have the 3D STEP modeling, it's really easy to detect an error in a through-hole footprint. But for surface mount, you put the 3D model on a surface mount pattern, you look at it and you think, "Well, I don't know if it's right or not. Is the toe correct? Is the heel correct?" A basic understanding of terminal lead style rules and their respective solder joint goals would help you make that determination.

If I were to do a class on land patterns the first topic would be that 80% of the parts on a circuit board are chip resistors, capacitors, inductors, and filters. I would say, "Let's design a pattern for each package size because there's not one magic formula." An 01005 chip package requires a unique land pattern, then then you have a 0201 and it requires its own unique toe, heel, and side. You have a 0402, a 0603, a 0805, and they all require unique patterns.

The IPC-J-STD-001 standard is my leading document. When I took the IPC-J-STD-001 class, I learned how to hand solder and learned all about solder joints. I learned a lot of information about solder joint acceptability for assembly. The very first sentence in IPC-7351 land pattern guideline reads, "This document should adhere to the IPC-J-STD-001." Actually, it doesn't, as far as solder joint goals for various chip sizes and gull wing pin pitches. However, the IPC-7351 mathematical model for calculating an accurate land pattern has stood the test of time for the past 34 years, but the solder joint goal values for toe, heel, and side need to be updated for microminiature components and fine pitch packages.

**Matties:** How are the datasheets? When you come in and you're dealing with a new component, do you validate the datasheets on your own? Do you trust them? What's your strategy there?

**Hausherr:** The datasheets provide the package dimensions. And most datasheets today provide the recommended pattern. Some of the patterns are getting so complex that it's like designing a mini circuit board. It takes five hours to design one pattern. Today's manufac-

SUBSCRIBE

## Subscribe to the Polarinstruments YouTube channel for helpful impedance and stackup videos

#### PCB Signal integrity tools for design & fabrication

- Impedance & insertion loss modeling with Si9000e

- PCB stackup design & documentation

- Test systems for controlled impedance & insertion loss

- · Application notes on a wide range of Si topics

polarinstruments.com

turers are designing tiny 7 mm x 5 mm packages with a gazillion pins underneath them. They're bottom terminal only, and every pin seems to have a different size and location with a different solder and paste mask. They'll have one page in the datasheet set aside just for the pad dimensions, another page for the pad locations, another page for the solder mask dimensions, solder mask locations, the paste mask dimensions and another of the paste mask locations. It gets to be really, really technical with a lot of geometry mathematics involved.

Dieter Bergman and I tried to figure out how much money is being spent in the industry in library part creation for schematic symbols, footprints, and 3D models. We looked worldwide at all the companies, patterns, and boards that are being made. We concluded that to be an expense of about \$1 billion a year. The \$1

billion includes salaries, computers, CAD tool software, furniture, training, and compensating for errors and mistakes in library creation. A lot of revenue goes into PCB library creation globally and the main reason why the yearly expense for creating PCB libraries is so high is because most companies create their own library parts using their company rule set and that contributes to massive duplication of effort. However, we can greatly reduce cost and error rate by having access to all the schematic symbols, standard package dimensions, non-standard manufacturer footprints, and 3D STEP models in a single location on the cloud. This is a tremendous never-ending project as the number of new component packages every week is overwhelming. This year, over 20 million brand-new electronic component part numbers will be introduced.

Digi-Key currently has 11.5 million parts on its website. The Valor Parts Library contains over 35 million part numbers for PCB mount components. SiliconExpert supports datasheets on over 1 billion electronic part numbers for both current and obsolete parts. That's a lot of symbols, footprints, and 3D models.

The concept of reducing cost and errors of PCB library creation is a reality. You need a software program that only requires package and terminal lead dimensions, and tolerances and a user-defined set of options to define all your personal library construction rules. This way you get consistent quality in your PCB library. Also, you can change any of your personal options or your CAD tool and regenerate your complete

PCB library from scratch using your collection of package dimensions and tolerances.

**Matties:** Well, this has been really good. Any final thoughts, Tom?

**Hausherr:** I have one thought. In your PCB library calculator tool, you have a nominal 1:1 scale image package outline

and terminal leads; when the terminal leads fall somewhere on the pad, you'll be fine. It's when the pad falls away from the terminal lead that you run into trouble. And that's where the Valor PL and the 3D model can reduce errors.

In our software calculator tool, Footprint Expert, we draw the rectangular shape of the terminal lead on the pad, so when the user calculates the IPC pattern, enters the manufacturer component recommended pattern dimension, and the pad falls off the terminal lead, you must go back to the IPC pattern. In this case, the manufacturer pattern dimensional data could have a typographical error.

IPC's mathematical model for land pattern calculation comes all the way from the 1987 release of IPC-SM-782 for 18 years, into the IPC-7351, all the way up to today. Now, things are changing; tolerances used to be robust, but tolerances today are getting smaller and smaller, because the manufacturers are getting better, high-quality machines to manufacture their component packages.

I hear this all the time: "I want to use a single 0603 footprint for all my 0603 resistor packages. There are about 22 manufacturers who create 0603 resistors, and I want to use the same footprint pattern and 3D model for all of them."

Well, guess what? You could do that, but you must use the same exact package dimensions and tolerances. If one manufacturer's dimensions and tolerances fall out of your master set, then throw that manufacturer off to the side. All of your manufacturers for an 0603-resistor package should have the same dimensions and tolerances. There is no standard for resistor package dimensions and tolerances, but if we band together and reject packages that fall outside the mainstream, a de facto standard will eventually emerge. Most chip package dimensions are standard. The package tolerances make a messy PCB library where it generates all these different patterns for an 0603 pattern for a resistor. The main reason for standardizing package dimensions and tolerances is to reduce the number of footprints in your CAD library. But the big problem is that you can use one manufacturer in your BOM, but the assembly shop may save you money by using a different manufacturer's chips that they have in stock. That's okay, as long as the parts they use match your package dimensions and tolerances.

I want to mention that the package and terminal tolerances affect the resulting pad stack size and placement. You can have identical nominal package and terminal dimensions, but different tolerances will produce different footprints. The IPC mathematical includes the tolerances in the land pattern calculation to allow proper solder joints in case the component is delivered in the minimum, nominal, or maximum material condition. However, I've heard from many assembly shops that most component packages are delivered in the nominal material condition. Therefore, you can use a tolerance of zero and greatly reduce the size of your PCB library. If you must use tolerances, standardize them.

**Matties:** Thanks for your time, Tom.

Hausherr: Thank you. I enjoyed it. DESIGNOO7

## Shell, C3 AI, Baker Hughes, Microsoft Launch Open AI Energy Initiative

Shell, C3 Al, Baker Hughes, and Microsoft announced the launch of the Open Al Energy Initiative (OAI), a first-of-its-kind open ecosystem of artificial intelligence (AI)-based solu-

tions for the energy and process industries. The OAI provides a framework for energy operators, service providers, equipment providers, and independent software vendors for energy services to offer interoperable solutions, including Al physics-based models, monitoring, diagnostics, prescriptive actions, and services, powered by the BHC3 Al Suite and Microsoft Azure.

The initial OAI reliability solutions offered by Shell and Baker Hughes enable interoperability between BHC3 Reliability, OAI modules, and existing industry solutions for such applica-

tions. Solutions available today include proven and tested equipment- and process-specific modules with pre-trained Al models, codified subject matter expertise, low-latency data thermodynamic connectors, and operating parameter libraries, global health monitoring services, deep diagnostics, failure prevention recommendations, and prescriptive actions.

(Source: Business Wire)

## Avoiding 'Blushing' and 'Bubbling' in Conformal Coatings

## **Sensible Design** by Phil Kinner, ELECTROLUBE

The performance requirements of conformal coatings continue to become ever more challenging as electronic assemblies are becoming smaller and smaller and subjected to increasingly hostile operating environments. The perfect conformal coating would retain high elasticity at both high and low temperature extremes and would maintain its properties at high temperatures with no out-gassing. It would also provide an excellent barrier to moisture, both in terms of humid environments and where there is a risk of liquid water splash. It would be highly resistant to solvents and corrosive gases but be easy to remove when repairs or modifications need to be carried out. Ultimately, the perfect coating would be intelligent, self-applying and, of course, free of charge—but then that's a whole different ball game.

In this month's column, I will revisit a couple of general enquiries we have received about "bubbling" as well as the less common appearance of cloudy white patches following the application of a conformal coating.

## Blushing

Naturally, we are all aware of the many potentially problematic encounters that can occur when using conformal coatings. The usual suspects tend to be contamination leading to corrosion, cracking, blistering, fisheyes, de-wetting, and so forth. However, one of the rarer problems that can occur is "blushing." If you have the misfortune of discovering that your coating isn't as clear or transparent as it should be, and instead, looks dull and cloudy white, then the chances are you have stumbled upon this particular coating issue.

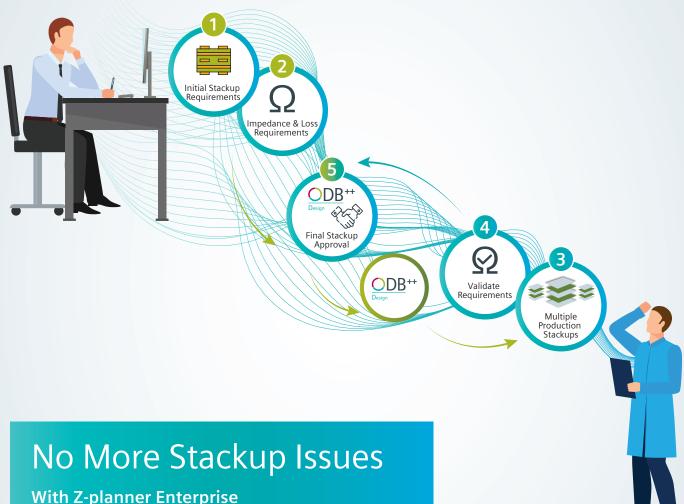

#### With Z-planner Enterprise

It's essential to get your PCB stackup design correct to minimize schedule and cost risks to your project.

Z-planner Enterprise helps you design first-time optimized stackups that meet your specs and budget, plus you can map your design to your supplier's available materials and process capabilities. With the digital twin software provided by Siemens, you can get your designs right the first time.

The main reason why coatings can become milky is largely due to moisture absorption. High levels of atmospheric moisture can create havoc with certain solvent-based materials. As the solvents evaporate from the coating, a cooling effect is experienced. If this cooling effect drops the coating below the dew point, then water will condense onto and into the coating as it dries. This can range from a reversible cosmetic effect (heat it up and the discoloration should disappear) to problems with the coating developing adhesion, or its full protective properties. Blushing can be identified when the conformal coating becomes cloudy, hazy, or milky in appearance. Humidity is a big issue, especially if it exceeds 65%. Equally, low temperatures can also wreak havoc at lower than 15°C. Issues that arise from assemblies/components stored in environments with excessive moisture can be addressed by baking the boards.

Some of the problems that can arise from blushing include:

- Surface tackiness

- Poor adhesion

- Incomplete cure

- Poor adhesion with second coating

- Dull, matte finish

Blushing can occur when using aerosol coatings. To avoid blushing when coating via aerosol, there are some important points to remember. First, there is no need to shake the aerosol can before use, as this can add bubbles to the mixture which can then be transferred to the board. The board should be at a 45-degree angle to the can, (e.g., if the board is flat, the can should be at 45 degrees) and around 20-30 cm away from the can. Spray the board in a continuous steady Z motion, coating evenly. The board should then be rotated 90 degrees, the coating applied again using the same motion, and the board rotated again, repeating the process until you have rotated the board a full 360 degrees. This allows an even coating of the correct coating thickness and ensures the

coating can cover raised components and leads from different angles, thus ensuring the best coverage possible. A turntable can be used to aid this process.

Other factors to help prevent blushing include maintaining a stable humidity and temperature in the production environment. At Electrolube, we recommend humidity between 50-65% and an ambient temperature environment between 15°C and 25°C to help combat blushing. Ensuring adequate time between coating and cure is also advisable to allow solvents to evaporate fully. The use of slower thinners can also assist with the potential reduction of evaporation/ condensation to reduce blushing incidences. Baking assemblies following the cleaning process can also eliminate moisture, as well as ensuring all storage atmospheres and containers are sufficient against moisture.

The quality and performance of a conformal coating material could also be compromised according to the method of application. This is commonly encountered when a product is transferred from one circuit manufacturer to another; for example, a product may be dipcoated in one country but selectively coated in another with the specification requiring that the same material be used at both sites. The problem that arises here, however, is that using a material formulated for dip coating in selective coating equipment can result in poor yield due to it being excessively fast drying, leading to bubble entrapment. You want fundamentally different behaviour from a material in a dip-coating application than in a selective spray application. One of my customers spent six months trying to solve a bubble issue internally, without realising that the root cause of this problem lay in the material formulation. Working with the customer, it became clear that by changing the solvent blend, the bubble entrapment issue could easily be resolved. Moreover, this solution simplified the process and reduced the cycle time significantly. And since the non-volatile formulation remained the same, there was no need to re-qualify.

#### **Bubbling**

When solvents or air become trapped and can't escape the coating material, the chances of bubble formation are more than likely. Bubbles in a conformal coating can lead to product reliability issues further down the line and even possible failures. The IPC specification allows a dry film thickness of 30-130 microns, the greater thickness being achieved by the application of multiple coating layers. Trying to achieve a 130-micron dry film thickness from a single selective-coating process with a solvent-based acrylic material is a recipe for disaster and is likely to result in excessive bubble formation, film shrinkage, coating de-lamination and additional stress on components. The result is poorer protection, rather than an improved overall level of circuit protection. Aiming for a uniform 30-50 microns and focusing on achieving perfect coverage at each application is a much better approach to improving the protection of electronic circuits. Achieving the correct coating thickness is important. Bear in mind that if the coating is too thick it can lead to entrapment of solvents in areas where the coating does not fully cure. Similarly, it can cause the coating to crack as it cures, as the result of changes in temperature, or due to mechanical shock and vibration.

Conformal coatings protect electronic assemblies from harsh environments by sealing off the electronics from contaminants and environmental factors that can lead to reliability issues and failures. For coatings to be effective, they need to uniformly cover the entire component without moisture, fluid, or outside impurities present. While it might be tempting to use shortcuts either to reduce costs or to speed up production, there will inevitably be a price to pay. Know the limitations and/ or special properties of the materials you use to coat electronic assemblies and abide by the correct procedures. Still have doubts? There are experts on hand at Electrolube who have seen it all before and who can steer you in the right direction. DESIGNOO7

Phil Kinner is the global business and technical director of conformal coatings at Electrolube. To read past columns or contact Kinner, click here. Download your free copy of Electrolube's book,

The Printed Circuit Assembler's Guide to... Conformal Coatings for Harsh Environments, and watch the micro webinar series "Coatings Uncoated!"

#### **How Unmanned Underwater Vehicles Could Become Easier to Detect**

Detecting the presence of an unmanned underwater vehicle (UUV) is usually achieved by intercepting the noise radiated by its propeller. In a noisy harbor, this task is hindered because the acoustic signature of a UUV and the noise in the local environment often present too much signal complexity for current technologies to process.

That may be about to change. Researchers at Draper, Massachusetts Institute of Technology (MIT) and Woods Hole Oceanographic Institute (WHOI) have developed an acoustic remote sensing method for high-precision propeller rotation and speed estimation of UUVs.

A state-of-the-practice technique for identify-

ing the presence of ships is by analyzing passive acoustic data with the Detection of Envelope Modulation on Noise (DEMON). In the study, the authors set out to isolate and characterize motor noise, so they focused on brushless DC (BLDC) motors because of their prevalence in UUV propulsion systems.

In field experiments, the new method outperformed the DEMON algorithm. When boats passed by the UUV, the new method could detect the motor noise, but the DEMON spectrum was dominated by the interfering boats' propeller noise. The new method can also apply to other robotic platforms that are powered by mass-produced BLDC motors. (Source: PRWEB)

# Managing Footprints with Integrated EDA Tools

Feature by Matt Walsh

SIEMENS DIGITAL INDUSTRIES SOFTWARE

Electronics companies are always under great pressure to continually grow and innovate. In addition to navigating ever-accelerating design cycles, they must also address and overcome generational complexities associated with their products, the underlying components they use, and the human capital accountable for delivering on time and on budget. Electronics firms can ill afford the time and resource inefficiencies associated with manually correcting design errors, poor library data integrity, or other inconsistencies leading to missed deadlines or even costly re-spins.

The quality of eCAD libraries—or, more specifically, the quality of the underlying logical and physical models—plays a pivotal role in stemming the challenges of delivering a successful electronics product to market. In fact, the eCAD library affects every process from PCB layout to PCB manufacturing and assembly.

The Siemens PartQuest cloud-based application is a gateway to a large collection of compo-

nent technical content for electronics design. This addresses five critical factors relative to best-in-class PCB library solutions:

- 1. High-quality eCAD model content.

- 2. Symbol and footprint creation.

- 3. Library management.

- 4. Standards.

- 5. Integration with Xpedition and PADS Professional.

In October 2020, Siemens released the Part-Quest Vault, consisting of eCAD models (symbols and footprints) for over 1 million parts. These pre-made models are entirely created, validated, and maintained by Siemens. A rules engine consisting of validation logic and thousands of checks are run against model content to confirm construction correctness, which provides end-customers with peace-of-mind when using this content. Further, the Vault is parametrically or keyword searchable, which simplifies the identification of the precise part to meet a product design's requirements, and the Vault is expected to contain 100 million parts by the end of 1QCY21.

Gain knowledge, save time and improve your bottom line with ASC's

# FREE RESOURCES

#### **WEBINARS**

Attend weekly free webinars focused on different PCB topics

#### **eBOOKS**

Download concise and relevant books written by the ASC Experts

#### **EXPERTS BLOG**

The ASC Experts help you learn more about advanced PCB technologies

#### **ONLINE DFM**

Upload Gerber files and get results back in just 60 minutes

#### American Standard Circuits

Creative Innovations In Flex, Digital & Microwave Circuits

www.asc-i.com | (630) 639-5444

There are inevitably instances where premade eCAD model content might not be readily available. For these scenarios, users have one of two options. First, users can request model content be constructed; turnaround time is typically less than 24 hours. This is presently a free service. Second, PartQuest has a robust part-builder capability. Whether a simple op amp or significantly more complex flatpack with multiple terminal groups, the "Create Footprint" capability guides users through easy-to-follow wizards and templates (including tool tips) to create content that is correct by construction.

Whereas library content management is traditionally conducted via desktop authoring tools, Siemens has added a new dimension, allowing users to create cloud-based projects to manage library content sourced from the cloud. This valuable functionality is a lightweight library management tool for storing and managing library data. Content stored in projects can be quickly downloaded for use on desktop capture-and-layout tools, either in bulk, or on a single part basis.

We are particularly conscious of industry standards. For example, footprints created in PartQuest are constructed according to the IPC-7351B standard, which establishes requirements for surface mount device (SMD) pad dimensions in PCB footprints. The part builder footprint wizards also support the JESD30I standard (for package outline, terminal types, and terminal position classifications), and the JEP30-P100 JEDEC standard (for shape definitions and the terminal vertical dimensions).

PartQuest is evolving to meet the needs of the PCB design community. In fact, later this year, the solution will add support for multigeneration footprints based on customerdefined custom rules. Here's why this enhancement helps PCB designers: While manufacturing technology has evolved a great deal over the past decade, the IPC-7351B standard has not. For example, the land pattern used for a