# PGB00 MAGAZINE

**AUGUST 2019**

# WET PROCESSES

NH<sub>3</sub>

better products through improved chemistry

# OUR LIBRARY IS ALWAYS OPEN

Registered members of my I-Connect007 have 24/7 access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to Complex PCBs.

Enrich your mind and expand your knowledge! Download these popular titles with just a click.

They're pretty awesome!

# Your life just got better.

This book will teach you how to save time and money, reduce frustration, and make your job easier!

DownStream Technologies

I-007ebooks.com/doc

**DOWNLOAD NOW**

# Wet Processes & Plating

In this issue, we explore plating, including the chemistries and processes that make up traditional subtractive etch and plate. We also investigate the confluence of smaller dimensions, reduced pollution, higher throughput, and improved reliability as they relate to wet processes and plating. Further, we address some of the emerging processes for higher-performance designs and new equipment to implement modern techniques.

10 The State of Plating by Marc Ladle

- 20 Chemcut: Wet Processing Equipment for the Long Haul Interview with Rick Lies and Jerry Reitz

- 28 Putting Green Into a Brownfield Facility Interview with George Milad

- 36 The Advantages of Non-sludge Acid Copper Products Interview with Mike Wood

from Happy Holden

44 Pollution Prevention Techniques: Rinse Water Reduction by Peter Moleux with contributions

4 PCB007 MAGAZINE I AUGUST 2019

# The only thing constant, is change.

-Heraclitus

At Eternal Technology Corporation, we value disruptive innovation as an answer to change. We believe that those who choose to disrupt and innovate stay relevant; those who don't, run the risk of becoming obsolete. Staying relevant means staying connected: internally with our employees and partners, externally with our customers, and globally with emerging trends and markets.

PLEASE JOIN US IN WELCOMING OUR STRONGEST PARTNERSHIP TO DATE.

IEC IS NOW OUR SOLE NORTH AMERICAN DISTRIBUTOR!

Eternal Technology Corporation 1800 Touchstone Road Colonial Heights, VA 23834 U.S.A TEL: +1-804-524-8555 https://www.eternal-group.com bob.ferguson@eternal-us.com International Electronic Components Inc. 809 Aldo Avenue, Unit 104 Santa Clara, CA 95054 U.S.A. TEL: +1-855-225-9333 https://www.ieccan.com chuck.williams@iecus.com

#### AUGUST 2019 • ADDITIONAL CONTENT

#### SHORTS:

**Red Wine May Hold the Key** 9 to Wearable Electronics

- 39 **Mobile Performance Report Shows** Incredible Speeds on 5G Compared to LTE

- **New Filter Enhances Robot Vision** 43 on 6D Pose Estimation

- **Cardiff Delivers Compound** 55 Semiconductor Breakthrough

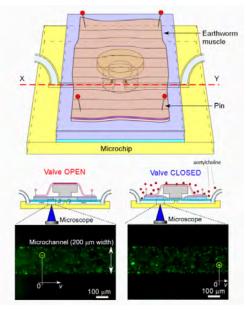

- 69 Cyborg-like Microchip Valve Driven by Earthworm Muscle

- 103 'Seeing' in Real Time

#### **DEPARTMENTS: 107** Career Opportunities

- 118 **Events Calendar**

- 119 Advertiser Index & Masthead

#### **HIGHLIGHTS:**

- 34 MilAero007

- **EINO07 Industry News** 70

104 Top 10 from PCB007

#### **ARTICLES:**

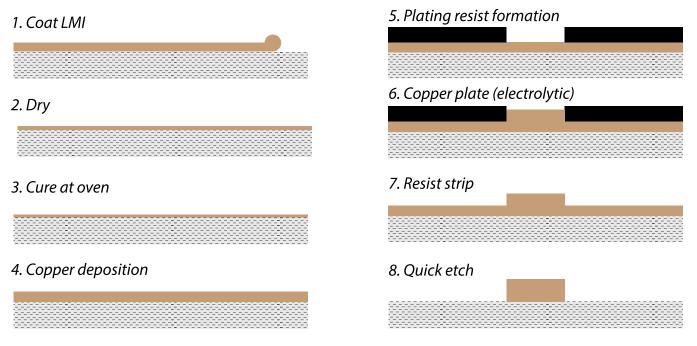

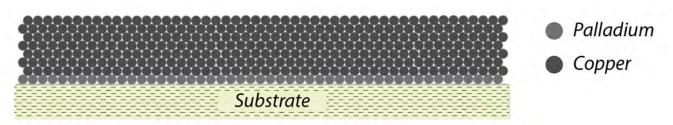

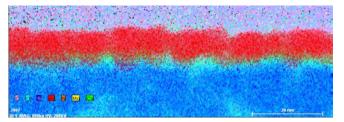

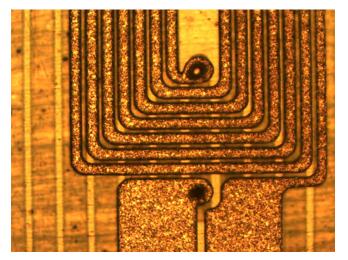

- **Innovative Electroplating Processes** 56 for IC Substrates by Saminda Dharmarathna, et al.

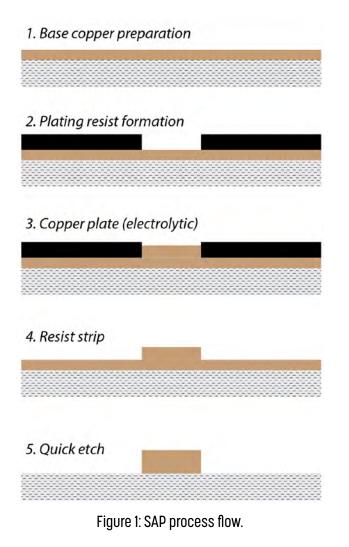

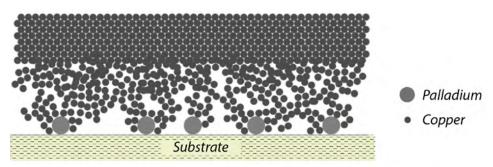

- **SAP Utilizing Very Uniform** 76 **Ultrathin Copper** by Steve Iketani and Mike Vinson

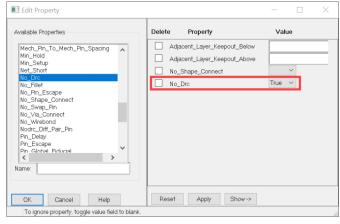

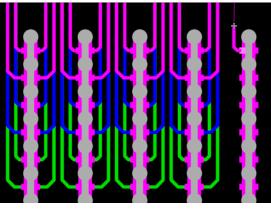

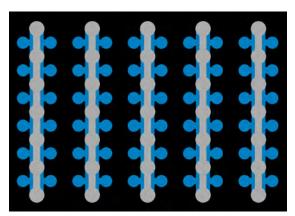

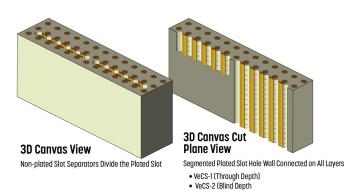

- Vertical Conductive Structures, 90 Part 3: Design Tool Techniques by Ed Hickey, Mike Catrambone, and Joan Tourné

- 100 Solder Mask Curing: **UV Bump Overview** by Nikolaus Schubkegel

#### COLUMNS:

There's An Art to Plating 8 by Nolan Johnson

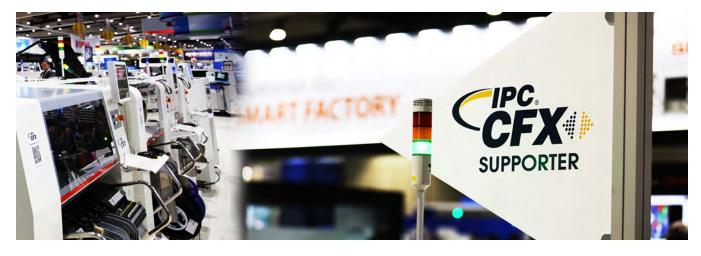

- CFX and Hermes: The Plug-and-Play 16 **IPC Standards Building Momentum** for Industry 4.0 by Dr. John Mitchell

- Via Hole Filling and Plugging, Part 1 40 by Michael Carano

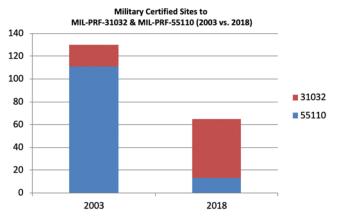

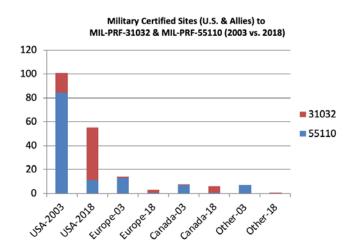

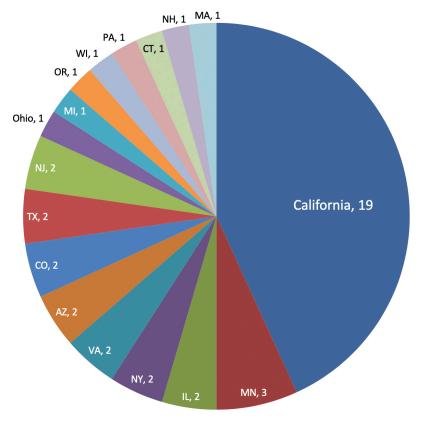

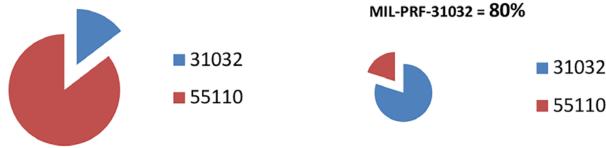

- The Past 15 Years: Changes to 72 MIL-PRF-31032 Certification, Part 1 by Mike Hill

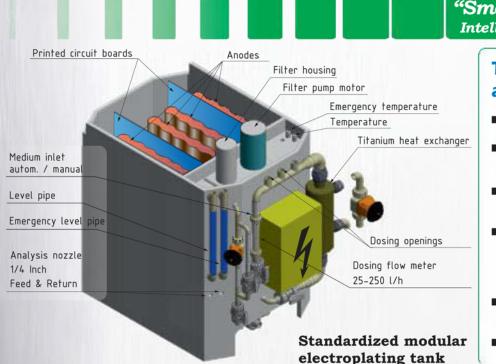

# **GalvanoMat<sup>®</sup>PCB**

The next generation of printed circuit board finishing

"A quantum leap"

#### Automated electroplating modules,

which can be adapted to the respective PCB product and the production flow ...

(Aspect Ratio: 1:20 / Format: 21" x 27", 530 mm x 680 mm)

**"Smart Manufacturing"** Intelligent networked systems

A BREE

Heiter

#### Technical advantages at a glance:

- Largely sewage- and exhaust free

- Fully automatic loading and unloading (optional)

- Energy efficient bath cooling and heating

- Integrated Industry 4.0 interface for easy integration into the manufacturing process

- Flexible operational software for job scheduling

- High Cu thickness uniformity

"Optimized for future production requirements with focus on quality rather than quantity!"

#### www.ludy.de / info@ludy.de

# There's An Art to Plating

#### Nolan's Notes by Nolan Johnson, I-CONNECTOO7

There's definitely an art to plating. Start with a generally planar substrate, then alternately put stuff on and take things off. Continue this in subtle variations until what you have is the stuff you want, where you want.

There are classes on plating (I'm talking about food now) pretty much everywhere. Escoffier, arguably the hub of French cuisine, offers an online course, and cooking schools, kitchen equipment retailers, and even community colleges offer training. The San Francisco Cooking School offers an in-person workshop on plating. In fact, the course description states, "By the end of the class, you will understand why the shape color and size of tableware is important when plating food." Ah-hah! The equipment and tools are as important as the raw materials: it doesn't matter whether we're

talking food or PCBs. Years back—at least in my part of the under-refined United States—plating food meant something large, bulky, and robust; that's how it was in our industry too during that era. But things change, and refinements are made. Even in the Wild West of the U.S., thoughtfully crafted plates with smaller portions appear on tables more often.

There are both differences and similarities when using food plating as a metaphor. As we become more sophisticated in the products we create, it isn't enough to run rough chemistries in crude facilities; one cannot deliver the fine details, small geometries, and precision that OEMs now expect from our fabricators worldwide. We can't be short-order line cooks any longer; we must become chefs of precision.

In this issue, we explore our kind of plating, including the chemistries and processes that make up traditional subtractive etch and plate. We also investigate the confluence of

smaller dimensions, reduced pollution, higher throughput, and improved reliability as they relate to wet processes and plating. Further, we address some of the emerging processes for higher performance designs and new equipment to implement modern techniques because the high-end techniques of today become the mainstream techniques of tomorrow.

Marc Ladle makes the first splash with his feature, "The State Of Plating." Dr. John Mitchell follows with his

column highlighting "CFX and Hermes: The Plug-and-Play IPC Standards Building Momentum for Industry 4.0." Chemcut CEO Rick Lies talks with publisher Barry Matties about "Wet Processing Equipment for the Long Haul." Then, in "Putting Green Into a Brownfield Facility," Uyemura's George Milad talks with me about the challenges and solutions in customizing up-to-date process chemistries to fit pre-existing facilities. Wrapping up the features, Cerambus' Mike Wood discusses "The Advantages of Non-sludge Acid Copper Products."

Columnist Mike Carano debuts his next series off the starting blocks with "Via Hole Filling and Plugging, Part 1." Of course, in wet processing, rinsing is a critical step, so Happy Holden's article addresses "Pollution Prevention Techniques: Rinse Water Reduction." And finally, Saminda Dharmarathna, et al., cover "Innovative Electroplating Processes for IC Substrates: Via, Through-hole, and Embedded Trench Fill." Mike Hill also debuts Part 1 of his column, "The Past 15 Years—Changes to MIL-PRF-31032 Certification, Part 1."

Continuing with the technical pieces, Steve Iketani and Mike Vinson post their research on "Semi-additive Process (SAP) Utilizing Very Uniform Ultrathin Copper by a Novel Catalyst." Then, we continue Part 3 of Joan Tourné's series on vertical conductive structures (VeCS) and design techniques, along with Ed Hickey and Mike Catrambone. Nikolaus Shubkegel makes his return to the magazine with his article, "Solder Mask Curing: UV Bump Overview."

Now, by all means, load up your plate! PCB007

**Nolan Johnson** is managing editor of *PCB007 Magazine*. Nolan brings 30 years of career experience focused almost entirely on electronics design and manufacturing.To contact Johnson, click here.

### **Red Wine May Hold the Key to Wearable Electronics**

Extracting tannic acid from red wine, coffee, or black tea led a team of scientists from The University of Manchester to develop much more durable and flexible wearable devices.

Previously, wearable technology has been subject to fail after repeated bending and folding, which can interrupt the conductivity of such devices due to micro-cracks. Improving this could open the door to more long-lasting integrated technology.

"We are using this method to develop new flexible, breathable, wearable devices. The main research objective of our group is to develop comfortable wearable devices for flexible human-machine interface," said Dr. Xuqing Liu, who led the research team. "Traditional conductive material suffers from weak bonding to the fibers, which can result in low conductivity. When red wine, coffee, or black tea is spilled on a dress, it's difficult to get rid of these stains. The main reason is that they all contain tannic acid, which can firmly adsorb the material on the surface of the fiber. This good adhesion is exactly what

we need for durable wearable, conductive devices."

The research was published in the journal *Small*. The overall impact of this new method could see a reduction in price for wearable technology, along with improvements in comfort and robustness.

The improved conductivity can allow technology developers to use more comfortable fabrics, such as cotton, to replace nylon. The technology can also allow for circuits to be printed directly on to the surface of clothing to make a comfortable, flexible circuit board.

(Source: The University of Manchester)

# The State of Plating

START

#### Feature by Marc Ladle VIKING TEST LTD.

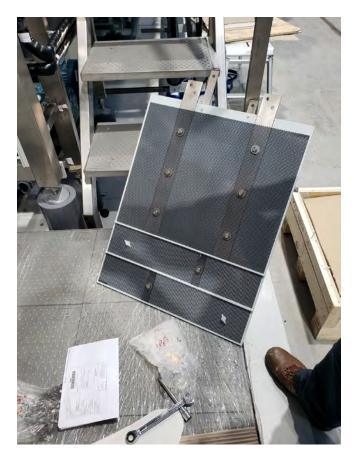

The current market for selling plating lines for panel and pattern plating circuit boards in Europe is not exactly huge. Since I have been involved in selling this type of equipment, the company I work for has probably averaged the sale of one machine per year. Normally, this has been due to the replacement of completely worn-out equipment or reinstatement of a factory after a fire. Within the last 12 months, we have sold the first line based completely on the requirement for advancing technology. Although this sample group is not large enough to see any real trend, I have a feeling that the European PCB industry is likely to see an increasing demand for machines that can achieve results to meet the demands of the newest ideas for electronic printed circuit design.

#### **Examples**

We rarely have a blank canvas to work with. In nearly every case, we must try to fit a quart in a pint pot. Space is the enemy when it comes to integrating the best available new technology into the footprint of the previous 20-yearold plating line. To make matters worse, it is not unusual to be asked to increase the output capacity of the equipment at the same time.

Increasingly, PCB design technology utilises buried and blind via holes and plated via fill is also becoming more and more common. The buried and blind holes mean that the loading on the plating equipment is multiplied by the number of different inner layer connections. The same technology means that equipment needs to deal with thinner and thinner materials. Plating copper via fill typically means the tank design must be larger, so it takes up more of the valuable space available and takes a long time compared to a traditional throughhole cycle. A typical through-hole plate might take 45–60 minutes where a via hole run could be 3–4 hours.

It is well known that the size of PCB factories in Europe is usually much smaller than the factories in Asia. Typically, this means there is only a single plating line available to production, and this one piece of key equipment must cover every type of work which goes through the factory. Compromises must be made, and

### THE NEXT BIG THING IN SOLDER MASK IS HERE!

"In my 34 years in circuit boards I never thought I'd see Inkjet solder mask, way to go Taiyo."

— Steve Franzino, Senior Process Engineer, Lenthor Engineering "We are excited to be the first Taiyo Inkjet solder mask customer in North America. The IJSR-4000 JM02DG solves the most challenging solder mask issues of mask in holes, mask on pad and registration."

— Rich Clemente, General Manager, Lenthor Engineering "Bringing Inkjet solder mask to the North American market has surpassed our timeline thanks to Lenthor's partnership."

— John Fix, Manager & Director, Sales and Marketing, Taiyo America

Phone [775] 885-9959 • www.taiyo-america.com • info@taiyo-america.com

usually, it is the work at the extremes of capability that suffer. For example, very thick heavy panels are hard to transport using commonly used top-clamping methods (they can drop out of the clamps unexpectedly). Very thin panels need extra support to stop them folding when they are dipped into the tanks and also to keep them in a stable position in the centre of the tank between the anodes (the plating will be too heavy on the side closer to the anodes and too thin on the side which is further from the anodes). For both problems, simple solutions are available, but the same fix does not suit both extremes at the same time.

The plating chemistry has also advanced when compared to the simple solutions and replenishment additives of years ago. Again, the major problem for smaller manufacturers is the sheer amount of variation in the work they have to put down the line and the fast turn arounds required by customers that prevent them from batching similar work together. The chemistry in a bath can definitely be tuned to provide even plating of a large area, such as panel plating where the whole surface of the panel is plated as well as the through-holes, but the same tuning is likely to make it very difficult to plate isolated details or very small plating areas. In the worst case, the additives have to be stripped out of the solution using a carbon filter and then added again to suit the next requirement.

#### **Solutions and Developments**

All of the previous cases are real examples I have come across during the last year, and they are very big problems for the companies involved. In some cases, the only practical solution is a larger factory and a second specialpurpose plating line. Development of hardware to meet the needs of the large range of challenges facing the plating operation has recently been quite strong. There are a number of features becoming more commonplace on new equipment and some that could also be retrofitted to existing equipment.

Zoned anodes are an interesting approach to help overcome distribution issues. Traditional soluble anodes using titanium baskets

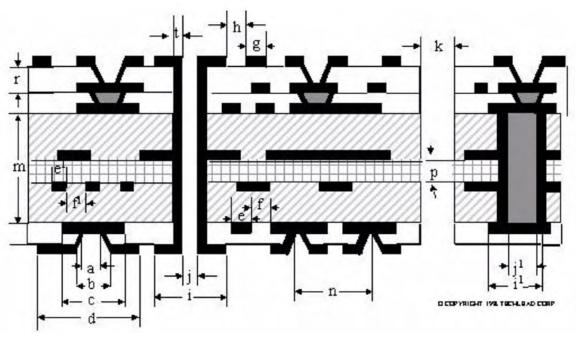

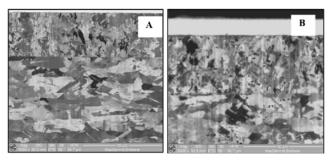

Figure 1: Zoned anode section.

filled with copper balls do not lend themselves to being able to control different areas of the plating window. They are typically hung on a single anode bar, and the plating current is applied evenly to the whole anode area. Using insoluble iridium mesh anodes allows zoning of the anode area, and you can control the current by depth by splitting the anode into sections and only applying the current to the section of the anode with a panel in front of it. This allows more accurate plating of different panel lengths without having to revert to floating shields.

Multiple rectifiers give the capability to split the plating window into sections across its width. This could be used to allow flight bars to run partly loaded with much more predictable results. This approach could be used alongside zoned anodes to provide an almost endless combination of ways to be able to split the plating window to achieve more accurate copper plating. Like the zoned anodes, this approach has many possible applications

Figure 2: Multiple rectifiers anode bar.

to enable the most flexible use of the plating window. This approach of larger numbers of smaller rectifiers is one approach that could potentially make vertical continuous plating (VCP) more appropriate for smaller batches of panels, opening up the possibility of using this type of machine to a much larger number of smaller factories.

VCP is becoming more widespread and offers a number of solutions to common plating problems. The main drive for the development of this machine type was to enable very even plating across the whole of the panel area. The work is driven through the copper cell in a continuous motion so that every part of the panel passes each anode, and in theory, is subjected to exactly the same high and low points of current density. It would be wrong to call the VCP process a new development as this machine type has been around for quite a few years now, but the application has certainly developed for an interesting range of processes. Electroplating very thin panels has always been difficult due to the nature of the "dip" process. If you use a conventional plating line, the panel has to be supported by a jig of some type to keep the very flexible panel in the correct position as it is lowered into the plating tank. In comparison, VCP can be formatted with Teflon guides, which keep very thin materials in an accurate position throughout their passage through the copper plating cell. Transport of 0.05-mm thick materials is possible using only top-clamping methods with no further support of the panel required.

For even more accurate VCP plating of thin materials, a system of top and bottom clamping has been developed. The idea is to keep the position of the material perfectly centred between the front and back anodes.

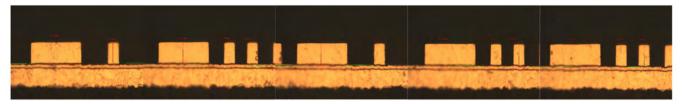

Figure 3: Top and bottom VCP clamps.

Figure 4: Top and bottom VCP clamps.

Plating chemistry is also an area that is presenting an opportunity for some new developments. Some of the most interesting results have come from being forced into a corner by the "only line in the factory" scenario. When you try something new, you pretty much have to design the experiment based on the copper solution in your plating tank. I watched a test using a pulse plating solution for very low area button plating test (just very few round pads being plated on an otherwise blank panel). The interesting aspect of the test is how good the results were based on simple calculations and guesswork. The first test was completed using chemistry designed for reverse pulse plating even though we intended to run a completely DC cycle. How much difference the chemistry makes is difficult to quantify based on a single test, so it was only much later when a test was completed using a conventional DC plating solution that we realised there were some potential benefits to using the chemistry from our first test.

#### Conclusion

aforementioned The cases provide examples of some of the developments that I have seen adopted in recent new plating lines. However, there are a number of other very developments that I cannot write about. Nondisclosure agreements apply to the most special of the plating processes and machines. When companies solve the toughest of problems, they are typically very reluctant to give away the key secrets involved, and with it, any possible technical advantage they have gained against their competition.

As a supplier of plating equipment, one of the pleasures of my job is that I am able to work

with some of the best engineers in the industry doing some truly interesting things—but I am sorry that I can't share more of it with you. **PCB007**

Marc Ladle is a director at Viking Test Ltd. To read past columns or contact Ladle, click here.

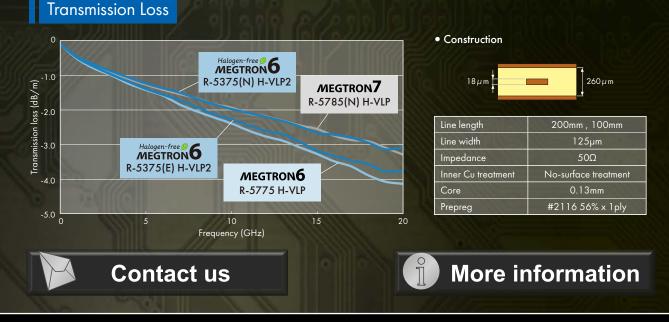

### Panasonic

Under development

Halogen-free Ultra-low transmission loss Multi-layer circuit board materials

### Halogen-free 26 6 NEW MEGTRON 6 Laminate R-5375(N)\* R-5375(E) Prepreg R-5370(N)\* R-5370(E)

\*Low Dk glass cloth type

#### Features

- Excellent HDI and thermal performance with Halogen free

- High speed and ultra-low loss material

- Low transmission loss

# R-5375(N)3.30.003R-5375(E)3.80.005R-57753.80.005

Dk

Df

@10GHz

#### Applications

• ICT infrastructure equipment, High speed networking(High-end server/ router, Optical network, switch), High layer count PCB, etc.

#### DISTRIBUTOR IN NORTH AMERICA MATRIX USA INC. TORONTO • SANTA ANA • SANTA CLARA • CHICAGO • MINNESOTA Visit our website at www.matrixusa.us

Partnering to go beyond.

#### Electronic Materials Panasonic Corporation

## **CFX and Hermes:** The Plug-and-Play IPC Standards Building Momentum for Industry 4.0

#### One World, One Industry

by Dr. John Mitchell, IPC—ASSOCIATION CONNECTING ELECTRONICS INDUSTRIES

IPC is removing barriers that hamper executives' ability to align their companies with Industry 4.0 by providing the building blocks for seamless machine-to-machine and machineto-ERP communications.

In April, IPC released IPC-2591, the Connected Factory Exchange (CFX), which is a plug-and-play standard for equipment communications. Earlier in June, IPC also released the surface-mount equipment communication standard IPC-HERMES-9852, The Global Standard for Machine-to-Machine Communication in SMT Assembly. You may have seen these two standards in action during our live IPC CFX/Hermes factory lines at IPC APEX EXPO 2019.

One line combined both digital SMEMA for machine-to-machine communication and CFX for output messages to a cloud server, and the second line utilized only CFX. The combined line ran printed boards of different sizes through a real-world manufacturing line using equipment from a variety of manufacturers. We also used boards of different sizes, so attendees could see the power of HERMES as equipment was able to communicate upstream to automatically adjust for the new board size.

The CFX line ran the same boards through a separate line to demonstrate how it alone could be used for machine-to-machine and machine-to-ERP communication. The CFX line also featured a solder paste dispensing robot and hand soldering tools communicating in CFX. Further, attendees were able to follow both production lines in real time from their mobile devices and laptops. This provided a glimpse into the possibilities of how to utilize the data reporting from CFX and HERMES in

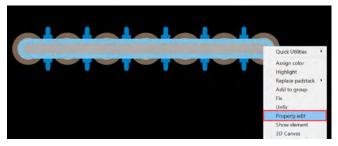

THIN CORE HANDLING • PC CONTROL • RELIABLE • LOW COST

**CLICK TO VIEW OUR UCE WET PROCESS LINE**

The leading European PCB Equipment and Parts Supplier

www.vikingtest.com sales@vikingtest.com

their own facilities as well as the power and simplicity of these two standards.

#### **IPC CFX and HERMES**

To say the least, the buzz around these two standards is palpable, and for six good reasons.

#### 1. CFX Provides a Level Playing Field for Manufacturing Companies

This includes manufacturing companies of all sizes and in any location. Setting up IPC CFX in existing equipment can be accomplished in a matter of hours—not days—and the SDKs developed to make it easier are available free of charge.

### 2. Both Standards Provide a Simple Messaging Protocol for Equipment

The messaging has been developed so that it can apply to new or legacy equipment. That means there's no more need for custom programming for machine-to-machine messaging or middleware. Eliminating the need for middleware reduces the eventual finger-pointing when adapters inevitably break.

### 3. The Standards Can Provide Significant Cost Savings

Developing a custom-built communications software, especially for multi-vendor equipment lines, can cost upwards of \$30,000 and take up to a full business quarter to implement. IPC CFX and HERMES are free to the industry, and companies have reported to IPC that they were able to implement CFX in less than one day.

#### 4. The SDKs Serve as a Building Block for Enhanced Production Tracking

IPC CFX and HERMES are written so that a company can easily and inexpensively add app-like functionalities for things such as materials traceability or quality improvement.

#### 5. CFX Is Flexible for Almost Any Piece of Equipment or Manufacturing Line

One company loaded CFX into hand soldering tools, and IPC is receiving inquiries on how to implement CFX into non-electronics manufacturing lines.

#### 6. Instant Access to Real-time Data on Any Piece of Equipment Worldwide

EMS sales representatives wanting to check availability of equipment for placing a new order or reporting a job status to OEM customers can view the activity of any piece of equipment in any facility, in any part of the world, in real time from their computer or handheld device.

This is just a sampling of the simplicity, value, and power of IPC CFX and HERMES.

#### **Collecting CFX Roadmaps**

Here's what's next for CFX. As interest in IPC CFX grows, we regularly receive questions about timelines for implementation/CFX roadmaps for equipment suppliers, software developers, and EMS companies. To address this, IPC is collecting industry roadmaps for CFX implementation, and we plan to begin com-

municating these to industry later this month.

If you would like to provide your CFX roadmap, complete the roadmap form, and you should encourage your suppliers to do the same. Submit your completed roadmap form to Chris Jorgensen, IPC director of technology transfer, at ChrisJorgensen@ipc.org.

#### Addressing Alternate Software Languages

IPC CFX was developed for .NET environments, but as the first version of IPC-2591 was under development, the 2-17 Connected Factory Exchange Initiative Subcommittee recognized the need to address software development kids (SDKs) for other languages in later versions. Groups are underway to develop SD-Ks for Linux, Python, Java, Node JS, and Labview. Once these SDKs are approved by the subcommittee, they will be available free of charge on the CFX GitHub website.

While the committee develops these new SDKs, they are seeking feedback from the industry on the languages your organization and equipment support. Provide your feedback through this brief survey.

#### Version 1.1 Coming This Year

To meet the needs of industry, the 2-17 Subcommittee has decided to put IPC-2591 on a twice-yearly revision schedule, and it has planned Version 1.1 for release by productronica in November. Version 1.1 will address new messages that the subcommittee was not able to include in the first version of the standard. Version 1.1 will also address the alternate language SDKs and include any necessary modifications to align with IPC-HERMES-9852.

#### How You Can Get Involved

There are ways you can begin aligning your company with CFX and HERMES today:

- 1. Bring both standards in-house and ask your software support team to review them for implementation in your facility or with your equipment.

- 2. OEMs and EMS companies should ask their suppliers for their CFX implementation roadmaps.

- 3. Nominate one or more people from your organization to join the 2-17 Subcommittee, so you can comment on the draft IPC-2591 v 1.1 before we release it. Sign up and demonstrate your support for CFX here.

- Check out a live demonstration. IPC is planning CFX/9852 demonstrations at SMTAI in September, productronica in November, and IPC APEX EXPO 2020 in January. PCB007

**Dr. John Mitchell** is president and CEO of IPC–Association Connecting Electronics Industries. To read past columns or contact Mitchell, click here.

#### Feature Interview by Barry Matties I-CONNECT007

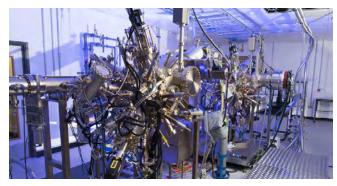

Chemcut CEO and General Manager Rick Lies speaks about the growth he has seen in the marketplace over his 18 years in the industry, and how Chemcut has been able to remain competitive in the PCB and photochemical milling spaces. Jerry Reitz, Chemcut's HES manager, also addresses the current shift towards zero-discharge facilities.

**Barry Matties:** Can you start by telling us a little bit about Chemcut?

**Rick Lies:** Chemcut's main market focus has been on making equipment for the wet processing industry that sprays chemicals, water, etc., across a moving conveyor populated with parts. We've been in business for over 60 years now. We started in the PCB and photochemical milling industries, which involves the etching of different metals to make small or big parts of various sizes and dimensions out of a wide variety of metals. Over 60 + years, Chemcut went from being a private company to being acquired by Schering, then Atotech, and back to Chemcut as a private company in April 2002, so it has been 17 years. Now, we're just an equipment manufacturer.

**Matties:** Is that an ESOP? Is Chemcut employee-owned?

**Lies:** It's not an ESOP, we are employee-owned; there are six of us now—we started with eight, but a few have retired and moved on. We bought it back from Atotech, so it went from Atotech back to Chemcut.

**Matties:** I remember all that transition.

**Lies:** And it has been going well. In the capital equipment business, you always have your

### **Excelon** Manufacturers of precision Micro-Machining Solutions for over 50 Years

Excellon Conv.

**COBRA II** Hybrid laser system

#### HS-1L DS Single-station, dual spindle high-speed system

689 6-station precision drilling and routing system

**136L** High accuracy and speed

**154L** Large panel applications

HS-2L 2-station, high speed

Move into the future with the latest innovations in Fabrication Technology from the Industry Leader!

www.excellon.com

ups and downs. We've lived through and survived those, and for the past three years, things have been going well. We've entered into some new markets, but our traditional business in the PCB industry remains strong. Then, the photochemical milling industry picked up, and we've started to get into semiconductors and glass etching for flat-panel displays, etc.

**Matties:** How long have you been with Chemcut?

Lies: I've been with Chem-

cut since I got hired at Atotech in July 2001, so since the inception of the new Chemcut.

Matties: And what did you do before Chemcut?

**Lies:** Before Chemcut, I worked 25+ years in a different industry, including at Avery Dennison, a worldwide leader in adhesive technology.

Matties: What is your background?

**Lies:** I have a degree in chemistry from the University of Louisville.

**Matties:** So, you came into Atotech in chemistry because that was a big play for them.

**Lies:** Yes. I worked with the chemistry and their equipment. They sold it as a package, and when the PCB market went over to Asia, they downsized the North American equipment.

**Matties:** Right. You entered at a time when the market was declining in North America.

Lies: Yes.

Matties: What were you thinking (laughs)?

**Lies:** Well, for me, it was all about location, location, location. We lived in State College, Pennsylvania, for close to 20 years the longest my wife Maribel and I had ever lived in one place before; that was the first time I made a decision based on wanting to stay somewhere (laughs). It was time to settle down.

**Matties:** That's great. It had to work because there were no options there (laughs). So, what was the challenge back then? At that time, Chemcut was six-years-old,

and by 2001, most of the industry was gone.

**Lies:** I think the challenge was to survive the first couple of years. Then, we wanted to keep our existing customers happy in PCB and photochemical milling and let them know that we were still there because Atotech was mainly interested in selling their chemistry, and the Chemcut equipment brand needed to be highlighted again as our main product line.

Matties: The brand got diluted.

**Lies:** Yes. When you look at Chemcut, the company was primarily known for its subtractive processes. Atotech's chemistry is more for additive type processes like plating. So, I like to say we divested ourselves of Atotech and had to get back out there with the Chemcut name in the subtractive area. That was good for us because we went from a large corporation to a small entity, and at the same time, there was the advent of websites.

**Matties:** High-speed internet came along right as that happened.

**Lies:** And that opened up the opportunity for Chemcut to market ourselves to the whole world. We didn't need boots on the ground or

22 PCB007 MAGAZINE I AUGUST 2019

Rick Lies

all of that printed material; we could get into Google searches. It was a different way to market your product, and it allowed us to market ourselves worldwide because our market is global.

**Matties:** I still see some of the original 547s out in the world.

**Lies:** Exactly. Chemcut equipment can last 10, 15, 20, and even up to 40 years. So, our equipment is still out there, chugging along. But that means your core customers—the equipment part of the business—change every year; you don't get repeat business quickly. We're starting to get repeat business for equipment we sold in 2003 and 2004 because, all of a sudden, that's 15 years ago. Eventually, we need a new set of customers for our equipment side every year. Now, product support and service generates a lot of repeat business. Over the past year, we probably have at least 500 customers worldwide that buy from us, anywhere from \$10.50 for a part up to \$1.5 million for a big line.

**Matties:** Hopefully, it weighs heavier on the high end (laughs).

**Lies:** Actually, the product support and service side of the business enables Chemcut to continue to exist and service our broad customer base worldwide.

**Matties:** And it's a lot less headache, too.

Lies: Exactly.

**Matties:** The market is still shifting, though. We're seeing more and more thinking of additive and the smart factory mentality coming into play. How is that impacting your business?

**Lies:** What we have seen in the market is a shift to more roll-to-roll processes as well as a shift to more additive processes for larger volume applications, which lend themselves to a smart factory mentality. At the same time, we have also seen a large demand for smaller

pieces of equipment for process development and smaller turns.

Matties: Right, and we're at a flex show.

**Lies:** Which is why we are showcasing this reel-to-reel equipment. What you see behind us is actually an additive process, making a semiconductor smart label in the California area, and then there's a plater that makes touch-screen products.

**Matties:** It's a diverse line. What sort of team do you have for engineering?

**Lies:** We have both mechanical and electrical engineers. We've been able to beef that up mainly with strong Penn State University graduates from the area. A majority of equipment is PLC controlled, but we still have a good section of the market that want the tried and true relay logic.

**Matties:** What is it about Chemcut that people might not know that you want to share with them?

### Our largest attribute is we make custom equipment to meet our customers' specific needs.

**Lies:** Our largest attribute is we make custom equipment to meet our customers' specific needs. We also have a lab where you can come in if you have an idea or a concept, or you've done it in beakers or dip tanks, and want to develop a larger-scale manufacturing process for commercialization. We cannot manufacture millions and millions of pieces, but we do have a lab where you can come in, and we can show you how to do that. We work with a lot of companies, developing processes for them, and have had people come up to us already today and say, "We're in R&D and have an idea. We need to do this." **Matties:** When you talk about the roll-to-roll process, how big is that? Is there a growing demand for that now?

**Lies:** More and more. We don't make the roll-to-roll, but we work with people who do and integrate it into our equipment for their specific manufacturing process.

**Matties:** The processing portion.

Lies: Right.

Jerry Reitz

#### Matties: Are you seeing a

higher demand for automation in North America? I know we're still talking low-volume, quick-turn, but it seems like there's something there.

**Lies:** I don't know if it's really automation. It has been more about the data gathering to control the processes, looking at it on a continuous basis, and making changes.

**Matties:** What about data gathering for legacy equipment? Is there a strategy to help customers retrofit?

**Lies:** At times. Truthfully, not a whole lot, as it is an expensive retrofit after the fact. Chemcut is highly backward integrated. A lot of the parts that you see on a piece of Chemcut equipment are made at our company. When you need to replace a part 30 years from now, we have our own molds that we make ourselves, and we've been able to supply parts that are over 50 years old.

**Matties:** We also talked a little bit about a boom in equipment sales earlier, and a lot of that was probably tied to the tax relief on the appreciation.

**Lies:** A portion of it is tied to tax relief, especially for the people who haven't re-tooled since

the early 2000s. So, there's the portion of people who sat on their money, and now they've re-tooled, but a lot of our growth is in new market areas. Over the past two years, a good portion of our growth has been in North America. Part of it has been re-tooling, but we have also seen new technologies and customers becoming a large portion of our growth.

**Matties:** When people come back and buy new equipment now, what do they look for? Has their equipment worn out, or are they

looking for upgrading capabilities?

**Lies:** It's a mixture. Some people don't want to change what they already have, and we can provide them that, but then they might want better control of their conveyor system, which we now have at the lower speed end, especially when it comes to reel-to-reel applications. Others might want better etching capability.

**Matties:** Along the way, it's still pumps and nozzles. What about the green movement? We're hearing a lot of zero-discharge conversations.

**Lies:** We've been involved with "zero-discharge" processes for our equipment for several years. How long have people doing zero discharge with our equipment, etc., Jerry?

Jerry Reitz: It has been nine or 10 years.

**Lies:** It's not necessarily new technology; it's out there, but it's about how to integrate it into your particular process.

**Matties:** It's about how you adopt it. What does it take for them to adopt it, and what's the advantage, other than not having to deal with the waste? Is there a financial gain as well?

# THINK TWICE BEFORE PICKING YOUR PCB DESIGN FLOW.

# PADS PROFESSIONAL IS SOFTWARE FOR THE MOST DEMANDING ENGINEERS

As PCB designs become more challenging, don't let your design flow become a career liability. PADS Professional is the high-grade software demanding engineers can count on to tackle the most complex projects.

AVAILABLE FOR A LIMITED-TIME PROMOTION STARTING AT \$8995\*

\*REGIONAL PRICING VARIATIONS MAY APPLY.

## EVALUATE TODAY

**Reitz:** There's absolutely a financial gain. They're not discharging their waste, so they're not generating it, which is definitely a plus. It's also easier for them to get permits to put in the equipment because local and state authorities like that movement, and some of our systems even recover the copper so that they can even get the copper back in full-sheet form.

**Matties:** When we visited GreenSource Fabrication in New Hampshire, Alex Stepinksi said he's not buying any copper for his plating; everything he's using is recycled. Why aren't more companies doing that?

**Reitz:** That's a good question. We try to push it with a lot of our customers, particularly those that are copper etching because it's a very simple technology that's available to them. However, I think it's still something new to them.

**Matties:** Is it that they're just unaware, or is it a complex system or a large investment? What are the obstacles?

**Reitz:** I think they just don't understand how to effectively integrate these types of processes and understand the full benefit of integrating such technologies.

**Matties:** Maybe this is something we should start promoting.

**Reitz:** Absolutely.

**Matties:** It would make a big difference. Everyone is looking to lower cost, and this is a surefire way to do it. Otherwise, we just etch it off and recycle it.

**Reitz:** Right. You reduce waste, supplies, liability, and your operating costs all the way around.

**Matties:** It makes good sense. You've both been doing this for many years. If you were to give fabricators advice about your area, what would it be?

**Reitz:** Size your equipment so that it's appropriate for your operation. Don't over-spec it or make it bigger than you need it to be. That's what I find: a lot of customers who think they need a huge piece of equipment when, in reality, smaller equipment will do the same thing and offer a lot less operating cost and environmental impact, which results in an overall win for the entire project.

**Matties:** Do better planning up front.

**Reitz:** Yes, with utilities and everything. A lot of customers who call us still believe that you only need one machine; you get it, you plug it in, and you're making circuit boards. However, they don't understand all that goes along with it; it takes a lot of planning.

**Matties:** So, the best advice is if you're getting ready to buy a piece of equipment, talk to you first not only about the equipment they want but also what they're trying to achieve with the equipment because it's easy to say, "I want this piece of equipment." And it's easy to sell it, but it's better served if we all talk about it.

**Reitz:** Exactly.

**Lies:** And there's another part to that, including the customer or the account, the equipment supplier, and the chemistry.

**Matties:** The chemistry supplier has to plug into this.

**Reitz:** Absolutely. It's truly a team effort. You have to work with the chemical and equipment suppliers, facilities, and environmental people; it's a group project. You can't just buy a machine and plug it in; it's a team effort.

**Matties:** That's good advice. Thank you very much for your time.

Lies: Thank you very much.

Reitz: Thank you. PCB007

### NO PROCESS CHALLENGE IS TOO **BG** TO OVERCOME.

#### **IPC TECHNOLOGY SOLUTIONS HAS YOUR BACK**

IPC Technology Solutions helps EMS providers and suppliers tackle increasingly complex operations and manufacturing challenges head-on with our five-prong approach:

Once an IPC Technology Solutions Expert uncovers the root cause of your issue and pinpoints the appropriate corrective action, they'll deliver a confidential technical report with recommendations for process improvements. They'll even educate your team on how to implement and sustain those improvements, and then follow up several months later to ensure our solutions are still working for you.

- **Enhance your operations.**

- Solve supplier challenges.

- Improve your bottom line.

For more information, connect with the IPC Technology Solutions Experts at **ipcvalidation.org/technology-solutions.**

# Putting Green Into a Brownfield Facility

#### Feature Interview by Nolan Johnson I-CONNECT007

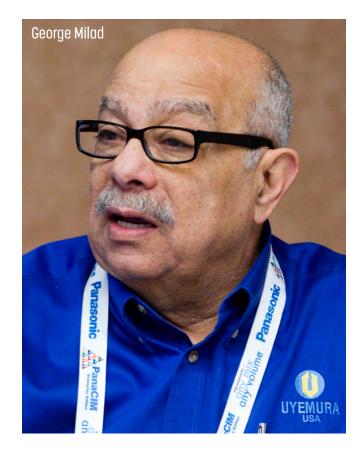

Nolan Johnson chatted with George Milad, national accounts manager for technology at Uyemura about what is driving change in the wet process marketplace and how chemistries must fit into next-generation product design while also meeting new environmental requirements.

**Nolan Johnson:** George, regarding changes in wet processes, some market drivers are moving, preserving margins, increasing yields, improving upon environmental concerns, and getting better capabilities and smaller features. From your perspective, where's the market for wet processes going and what's pushing it?

**George Milad:** Well, when you say wet processes, you're talking about chemical processes like board shop chemistries and where they're headed. Mostly, there are developments in surface finishing and plating; those two areas are quite active. For example, the IPC Plating Committee also publishes specifications, and we are in the midst of revising the ENIG specification.

**Johnson:** So, there's the chemical process side as well as the equipment that is used. Is there more action in one of those two areas than the other, or are both of them in motion right now?

**Milad:** As far as the equipment, there are tendencies to automate. Water usage and environmental control in wet processing are also evolving. Further, there are chemicals being used today that are not allowed on the REACH program environmentally. And there is an effort to minimize the use of these harmful chemicals, such as formaldehyde in electroless copper and cyanide in gold. There are new developments in surface finish to meet criteria, needs, and specific purposes, such as very fine-line work, as well as electroless copper plating via filling.

**Johnson:** In Richard DePoto's interview with Pete Starkey from IPC APEX EXPO earlier this year, one of the points that stood out for me was his comment that Uyemura works to drop the chemistry right into existing lines. It seems that putting in a new chemistry/wet process line to hold a different line and set of chemi-

## INNOVATION + PRECISION + RELIABILITY

0

- Processing for metals, thin foils, flexible glass and films

- Resist developing applications

- Cleaning applications

- Etching processes, including titanium and glass

- Aqueous based resist stripping

- Electroless plating processes

- Spray or immersion stations available for most applications

www.chemcut.net sales@chemcut.net

cals is a highly restrictive process for a lot of fabricators.

**Milad:** That is true. If I'm using chemistry from a certain supplier, and it's not meeting my needs, and I want to change to a different supplier, it is very important that the supplier can fit their chemistry into my existing equipment and does not force me to buy new equipment. I think that's what Richard was referring to.

**Johnson:** Pardon me for showing a lack of understanding of chemical engineering, but what goes into lining up the chemistries like that? For somebody who isn't a chemistry expert working with PCB fabrication, what is so different about the chemistries currently under development compared to what they used to be?

Designers are coming up with things that the present chemistries cannot meet, so they are moving forward with new chemistries to meet the designs.

**Milad:** If you're talking about under development, that is one thing. We were just talking about making the chemistry fit the existing equipment, but that's a different issue after the development of chemical processes to meet new board designs. Designers are coming up with things that the present chemistries cannot meet, so they are moving forward with new chemistries to meet the designs. The new designs have much tighter lines and spaces and much smaller holes for next-generation, 5G-type products.

**Johnson:** How do you change the chemistry for that?

**Milad:** We have a substantial R&D team that is always looking forward to the next challenge, so they are very busy developing new products. It's not changing chemistries; instead, it's a new set of products. Usually, they are designed to fit existing equipment. Sometimes, new equipment might be advantageous, but most of the time, they would develop products that fit the existing equipment.

For example, Uyemura is developing a gold bath that is cyanide-free, which is important; it's not a requirement today, but it will be in the near future. We're also developing chemistries that are formaldehyde-free because it's a hazardous chemical too. It is in use, and it's not prohibited, but people are expecting that it will be and should be. There's this direction based on meeting environmental needs, and then there is the development that is designed to meet more complex and sophisticated designs. We work on both ends to provide the chemistry for next-generation that will meet new environmental requirements.

**Johnson:** I know I'm talking in generalities here, but how long does it take to develop new chemistry like that?

**Milad:** The work in R&D is continuous. In general, Uyemura has about 60 people working in R&D, and they all have projects, looking forward, and are working to develop next-generation products. Sometimes, they develop them fast, but other times, it takes a while. It might work straight away when they try it, or they have to go back to the drawing board and redesign the product. It takes years to develop and test a product that is ready for the market.

The most important thing is that the market is constantly changing. This cycle is never going to end. It's not like all of a sudden, there will be no demands on the design and the environment; the demands are going to continue indefinitely. Once I meet the design criteria of today with my chemical wet process, the next generation of design is going to come, and I'll have to catch up with the designer and provide the chemistry they need. As soon as I'm there, they're on to the next design. It's an endless cycle of product evolution and environmental restriction, which are both crucial. With wet process, R&D departments move a lot.

**Johnson:** Are the designers driving the market and what happens in chemistry development? Do you involve them?

**Milad:** Maybe the statement that the designers are driving everything is not totally accurate. It's not the designer really, but the marketplace. The market says, "I need to go to 5G and make

a more sophisticated product. I need it to be smaller, lighter, faster, and able to carry more memory." That is market demand. Then, after the market demand, they go to the designer to design the product, and the designer is restricted by what is available to them. What's available to them is

what we (Uyemura) produce. We say, "We can give you these chemistries," and so they work with that and respond, "I need more," which forces us to consider new alternatives. Again, it's a continuous cycle.

**Johnson:** I understand what you're saying there, but I don't think it's an overstatement because the designers are the ones who have to take the conceptual market drivers and turn them into a real product. There is a point there where they are somewhat in charge. They're the implementers. Do you involve the designers in your market research?

**Milad:** No, we don't. We try to engage the OEMs themselves and understand what the needs are and what the next-generation product is going to look like, and then we acquaint them with our capabilities. We have a relationship with the OEM, which is designed to keep the OEM abreast of our capabilities and keep us abreast of their future requirements. Of course, everything comes into play; they want a more sophisticated product, or they

want to meet the environmental constraints. They say, "This is the chemistry you're using today. I would not be able to use that in a couple of years from now. You need to develop a replacement for it."

**Johnson:** As you're talking to the OEMs, do you find that they're more concerned about new capabilities and throughput?

**Milad:** Yes, they're concerned about everything that comes into play, including capabilities, throughput, cost, etc. They're trying to make

products, and they want to make sure that they're affordable and available. And they do not like a good product that's only made by one manufacturer. They want to have choices and be able to source overseas if needed. They want to get competing bids. So, if somebody

has the best process by itself, that doesn't excite an OEM; they want multiple suppliers. A single source doesn't excite them at all, even if the product is the best thing after sliced bread.

**Johnson:** If they're held captive to that and something goes terribly wrong, it's a big problem. That makes a lot of sense. How do you as primarily a chemistry supplier—work to make sure that those processes are as reproducible across the globe at as many different facilities as possible?

**Milad:** It's a challenge. Different parts of the world do things differently. Some shops that we refer to as "bucket shops" do work but they're not high-quality or reproducible. Then, you have very sophisticated shops that do very high-quality work as well as small, remote, and big shops. There is a very wide variety of manufacturers, and we work with all of them. A big part of what we do is tech service. Our employees set up the shop and say, "Here is what you have to do." But shops have different levels of engineering sophistication. Some

shops have very good engineering, while other shops have zero engineering and rely on the suppliers to give them all of the information.

Overall, wet processing development is being pushed by OEMs to meet sophisticated product requirements, which, at present, is where chemicals that are in use today are going to be phased out in a year or two. As a chemical supplier, we should be considering how we'll do that. How are we going to eliminate these hazardous materials?

**Johnson:** While minimizing the amount of equipment that the fabricator has to purchase to move forward as much as possible.

**Milad:** Right. Sometimes, if you have a totally unique concept, you have different equipment; then, the customer knows up front that they will have to purchase new equipment if they are going to use this process. But a lot of the processes that we develop are for customers who cannot afford to buy equipment all the time. They want the chemical process to fit into that existing facility with their current equipment. We try to do that as much as possible.

Johnson: Is that common across the industry?

### As a chemical supplier, we have competitors. But we collaborate when we're trying to write a specification.

**Milad:** I think so. As a chemical supplier, we have competitors. But we collaborate when we're trying to write a specification. After the specification is finalized, we compete against one another to try to sell our positive points, such as superior tech service or more robust chemistry.

**Johnson:** There has been a lot of work with Industry 4.0 at IPC, such as CFX and Hermes,

which were talked a lot about at IPC APEX EX-PO 2019 and since then. But it looks like most of the activity around CFX is on the assembly side.

**Milad:** I agree, but there is a lot of sophistication also coming to manufacturing related to software and automated equipment; it doesn't move as fast. There's always room for that.

**Johnson:** One of the big burning issues, especially in North America, is that most of the fabricators are nearing retirement age, and changing market needs are going to cause them to need to change their processes, which may or may not need significant investment in new equipment. Many of them seem to be uninterested in making that investment.

**Milad:** It depends. If you know you're going to make the investment and get a good return, you'll make it. But a lot of people are just milking what they have. I work with a board shop that has very poor equipment, and they struggle with it. They use old equipment to make products, and it's tedious. They put a lot of demands on the suppliers, saying, "Make your chemistry work for my old equipment." Last week, we were working with a board shop that acknowledged their equipment was not up to the task, but they wanted me to modify my wet process to accommodate that equipment. When that happens, sometimes, they're successful in making products, but other times, they're not.

You cannot have poor equipment and come to your supplier and say, "Make your chemistry compensate for my inadequate equipment." But we get that every now and then. Some board shops buy state-of-the-art equipment, have good engineering, and make very sophisticated products. Then, there are bucket shops making good money, but they work differently; they demand a lot from suppliers, like Uyemura, because they're trying to make a high-end product with sub-standard equipment.

**Johnson:** Thank you, George.

Milad: My pleasure. PCB007

# Get the spark you need to tune up your sales team.

When an engine doesn't fire on all cylinders, performance is limited. The same goes for your sales team. We provide the spark to get your sales to the next level ...and beyond.

> We've helped dozens of companies big and small improve their bottom line.

Learn how we can help YOU

3

€ 207-649-0879 ⊠danbbeaulieu@aol.com

## NASA Seeks Input from U.S. Industry on Artemis Lander Development

In a major step toward returning astronauts to the surface of the Moon under the Artemis lunar exploration program and preparing for future missions to Mars, NASA is seeking comments from American companies interested in providing an integrated human landing system to put the first woman and next man on the Moon by 2024.

#### Behind the Scenes of the Apollo Mission at MIT ►

From making the lunar landings possible to interpret the meaning of the moon rocks, the Institute was a vital part of history.

#### Math Invented for Moon Landing Helps Your Flight Arrive on Time >

They say the computers onboard the Apollo spacecraft were not even as powerful as your smartphone. So, how did they travel all that way, perform complex maneuvers in space, and return through Earth's atmosphere at just the right angle to splashdown in the Pacific Ocean?

#### Lockheed Martin Wins \$492M Contract for High-mobility Artillery Rocket System Launchers >

Lockheed Martin will produce High-Mobility Artillery Rocket System (HIMARS) launchers and associated hardware for the U.S. Army, U.S. Marine Corps, Romania, and Poland under a \$492 million contract, marking Poland's first acquisition of HIMARS launchers.

#### Of Art and Satellites 🕨

A quotation from The Golden Record 2.0—a play written for the NUS Arts Festival—and a

high-tech quantum device from the NUS Centre for Quantum Technologies (CQT) is now orbiting in space together.

### NASA Invests in 3D Printing for Aviation >

Additive manufacturing (AM), also known as 3D printing, is a promising new technology for all areas of aviation manufacturing. Additive manufacturing's flexibility in design and customization, cost reduction, and speed in delivering finished parts make it a perfect fit for creating parts used in aviation contexts.

#### 'Eyes' for the Autopilot >

Automatic landings have long been standard procedure for commercial aircraft. While major airports have the infrastructure necessary to ensure the safe navigation of the aircraft, this is usually not the case at smaller airports.

#### Collins Aerospace's David Adams Earns Dieter Bergman IPC Fellowship Award >

In recognition of his ongoing leadership in developing and promoting IPC standards on a global basis, IPC—Association Connecting Electronics Industries—bestowed a Dieter Bergman IPC Fellowship Award upon David Adams, Collins Aerospace, at the recent IPC SummerCom.

#### Aerospace Entrepreneur Burt Rutan to Keynote IPC APEX EXPO 2020 >

IPC APEX EXPO 2020 will feature aerospace entrepreneur and Virgin Galactic spacecraft designer Burt Rutan. During the opening keynote on February 4, Rutan will present, "SpaceShipOne: A New Era in Commercial Space Travel and Inspiration for Innovation and the New Race for Space."

**TECHNICA, U.S.A.** Fulfilling Manufacturing Needs Throughout the Electronics Industry

## **Chemstar: A Versatile Solution**

Wise has designed and developed this series of modular equipment to be suitable for a variety of processes used for flexible, rigid, or reel-to-reel printed circuits including:

- Chemical Cleaning and Micro-Etching

- Black Oxide

- Oxide Replacement or Alternative Oxide

- Desmear

- Direct Plating

- Electroless Copper

- Tin Stripping

- Finishing Surface Treatment (e.g. Silver, or OSP lines)

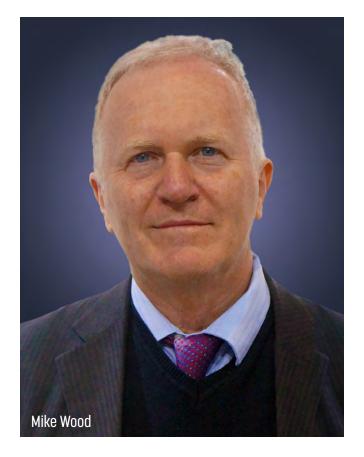

# The Advantages of Non-sludge Acid Copper Products

#### Feature Interview by Barry Matties I-CONNECTO07

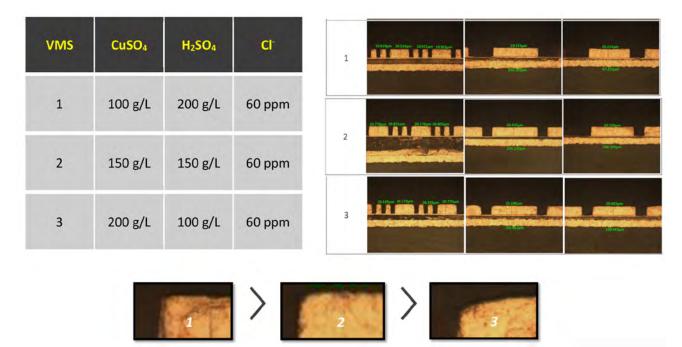

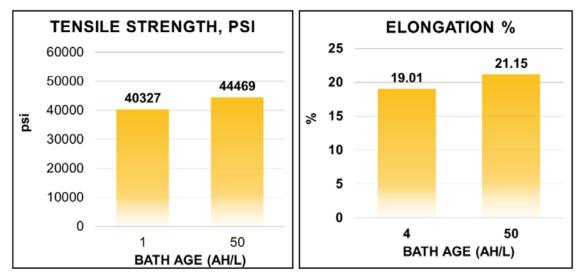

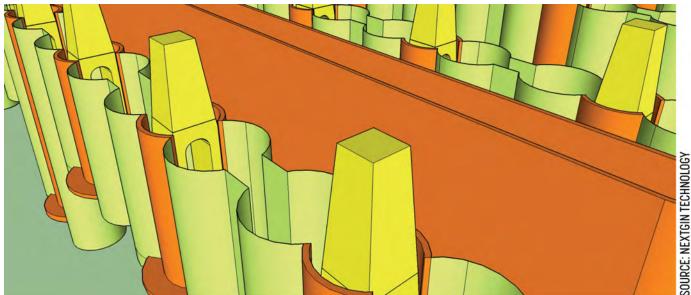

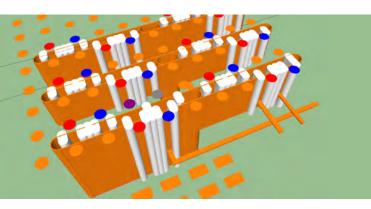

I had the opportunity to sit with Mike Wood, technical director with Cerambus Asia Pacific, at the 2019 CPCA Show in China. Mike discusses the acid copper product from Cerambus Technology Inc. that doesn't generate sludge during the plating process and operates at higher production output by using higher current density. This is important for the state of the vertical continuous plating (VCP) market in Asia, and trends he's seeing in that space.

**Barry Matties:** You told me a little bit about your technology for the elimination of sludge in copper plating. Can you give us a quick overview?

**Mike Wood:** The Cerambus acid copper product has many advantages. One main advantage is that it does not generate sludge as you are plating production. Typically, in about two months, the bottom of the baskets build in sludge. Along with this, the distribution on the lower portion of the VCP hoist line drops and the bottom of the panels have a lower thick-

ness because the sludge is building and shielding the nuggets at the bottom of that anode basket.

So, our product essentially has no sludge. For one year, you could run your process and not have to empty or clean the baskets. Most people clean every three months, and they have to take a week out of production time to pull the nuggets all out. But they still have to do production, so during that downtime, the PC shop sends panels to an outside job shop. The downtime and cleaning are very expensive. It's almost the same price as a full year of brightener when cleaning four times a year.

The second advantage is that without the sludge, you can have a better distribution, which also means higher plating amperage. This product will go above 30 amps per square decimeter (ASD) or 30 amps per square foot (ASF) current density and be very stable. I visited one customer, and in the past three months, the bath had no hand additions—only amp-hour replenishment at 38 ASF 24/7. To-day, with the high current density, new VCP machines in the market have increased the

## 'Integrate' QA solution by Gardien

#### **Continuous Integration, Continuous Improvement**

Driving your profitability, maintaining your sustainable growth and enhancing your brand is all made possible with Gardien's Integrate QA Solution which comes with proper documentation and real-time tracking of the process.

Designed for and valued by PCB manufacturers worldwide, Gardien's Integrate is an on-site, independent and unbiased validation of your board's quality. Its focal points are your product quality, efficiency and transparency. All your PCB manufacturing QA needs, be it AOI, electrical testing, final inspection or a combination of these are fulfilled by Gardien experts located globally.

With solutions built around your unique requirements and a pricing structure that perfectly aligns with your business interests, your costs are more predictable and easier to budget.

#### Find out more here: www.gardien.com/why-integrate

30 YEARS OF PCB INDUSTRY EXPERIENCE

eductor nozzles to a very high flow; it's closer to two liters per minute per nozzle. At that high velocity, many of our competitors get thin at the knee. We don't have that problem, so we can go to a very high current density from 34–38 ASF on these machines, increasing output by 20–30%.

Matties: So, you're adding capacity.

**Wood:** Yes. Three VCP machines give the same output as four.

**Matties:** Obviously, this is a proprietary solution. Why has it not been copied?

**Wood:** The technology is from the U.S., and we manufacture the concentrate there—and in a facility in Asia—so the key ingredients are manufactured and controlled by us. For five years, others in the industry have tried to copy it but have not been successful.

Matties: It sounds like the ROI is straightaway?

**Wood:** Absolutely. John Nash, my boss [and Cerambus president], has said to many customers, "Don't pay us for the brightener. Give us all of the savings that you receive from a lower operating cost." No purchasing agent has taken him up on it yet, but that speaks volumes.

**Matties:** I also understand that Cerambus continues to expand.

**Wood:** Yes, we're expanding into other markets. We're doing a lot of work in Thailand, and we're expanding into Southern Asia with the rest of the PC shops. We're also expanding into the more rural areas of China and business is going very well. We have a very good market share, and we're doing a lot with these advantages.

**Matties:** I would think your market share is increasing pretty quickly.

**Wood:** It is. We have a very high growth because of those advantages, and people are buying more VCPs.

**Matties:** When I spoke with John [Nash], he mentioned a new technical center. Can you talk about that?

**Wood:** Of course, we have our Dongguan facility that is a manufacturing and technology center, and we are planning to move from the San Jose area to the Las Vegas area with R&D and manufacturing.

Matties: How do you see the market right now?

**Wood:** Most people are going into the VCPs for consistency, and the end customer wants it. So, since our product works best with VCP, we see a little softening. But our sales continue to grow, and I see some more demand when I visit Thailand; there's a lot more demand there for buyers that want to have a fallback if any-thing happens regarding the trade war.

**Matties:** That seems to be a frequent topic of conversation in China. When you look at the Chinese market, how many years have you been here?

**Wood:** Cerambus has been here for many years, over 15. But over time, people haven't realized the advantages, and purchasing staff inside China are now understanding what the operating cost is compared to the price. So, instead of what the price per liter is if they analyze the full cost, that's when we expand our business.

**Matties:** The level of sophistication in Chinese manufacturing has increased as well.

**Wood:** Yes, we've witnessed that. One of the things that I've noticed for some of the automotive is they now use conformal microvias on the outside of the board. We had one customer who was running at 8 ASF with a competitor in VCP, and now they're running a throughhole and that microvia 6x5 deep at 27 ASF. So, our chemistry has some big advantages.

**Matties:** What advice would you give to a fabricator in China?

**Wood:** Right now, you have a lot of internal growth. I just heard that retail in China was at a 14-year low, so that may have an impact. There may be a slowdown that will consolidate the market. At this point, if I were a PCB company, I would continue what I was doing and look for cost efficiency and final yield. Often, the chemistry cost is nothing compared to the final yield; if you can improve 0.5%, then all of your savings would be there.

**Matties:** Those are all bottom-line dollars.

Wood: Absolutely.

**Matties:** Is there anything we have not discussed that you would like to share with the industry?

**Wood:** I believe the one thing that people are doing to lower their cost is to buy a piece of automated equipment-VCP systems. The advantage of VCP is if one anode is bad, you have another 99 of them, so you lose less than 1% of your thickness distribution on one side-one out of 100. But if you have a hoist and that anode is sitting in the middle of your panel, you can plate low thickness and create scrap. Right now, everybody is moving toward VCP because they want a high output with low coefficient of variation (COV). To pay for it, they want the highest plating amperage and plating speed, so the key area is efficiency. We can save money on metal consumption over many months and no anode sludge. I also see automation utilizing robots for loading and unloading of panels, and the equipment suppliers are doing a good job of taking advantage of improvements in design.

**Matties:** Well, we certainly appreciate your time today. Thank you.

Wood: Okay. Thank you. PCB007

## Mobile Performance Report Shows Incredible Speeds on 5G Compared to LTE

South Korean operator LG U+ held an edge over the competition in Seoul by delivering the fastest 5G speeds and lowest latency among all networks while also providing outstanding 5G data reliability, according to the first in a series of 5G First Look Reports by RootMetrics—the standard for mobile performance benchmarking by IHS Markit. The report discusses 5G performance by South Korean operators KT, LG U+, and SK Telecom, offering insights into the world of 5G and how 5G networks perform from the consumer's perspective.

#### Key takeaways from the report include:

- Each operator's median download speeds on 5G were much faster than those on non-5G mode or LTE

- All three operators were on 5G during at least 42.2% of RootMetrics download tests

- KT and LG U+ led the way with latency with both operators' 5G median download latency twice as fast as that recorded in non-5G mode

- Operator highlights: All networks show dramatic speed improvements on 5G

LG U+ had a 5G median download speed of 426.4 Mbps that would take only 12s to download a 600MB TV show. Although KT delivered the slowest 5G median download speed across all networks at 163 Mbps, it would still only take about 30s to download a TV show at this speed. Meanwhile, SK Telecom delivered a 5G median download speed of 286.9 Mbps.

(Source: IHS Markit)

# Via Hole Filling and Plugging, Part 1

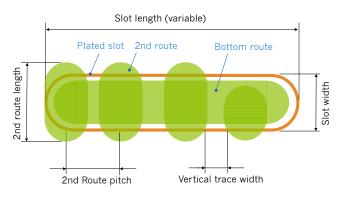

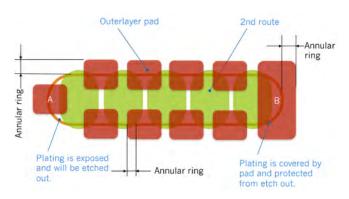

#### Trouble in Your Tank by Michael Carano, RBP CHEMICAL TECHNOLOGY

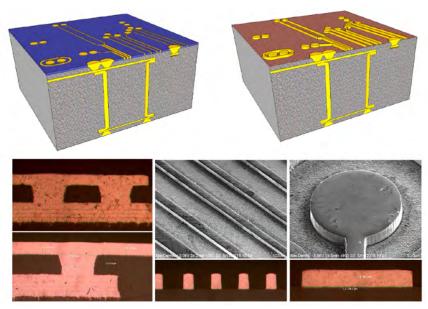

High-density interconnect (HDI) demands that vias that do not contain component leads be plugged with either a polymeric paste or electroplated copper. In this column, the technology drivers for via filling/plugging in the context of HDI are presented.

Performance-driven electronic systems continue to challenge companies in seeking a more innovative semiconductor package methodology. The key market driver for semiconductor package technology is to provide greater functionality and improved performance without increasing package size. As semiconductor die elements shrink in size, companies are seeking to further increase package density and enhance functional performance. This, in turn, drives designers to expand the current role of the interposer to interconnect both heterogeneous logic functions and homogeneous memory within a single package outline.

The package interposer is the key enabler; this is especially true as glass-reinforced, epoxy-based materials, and high-density copper interconnect capability will continue to carry a primary role for array configured packaging. From a PCB fabrication standpoint, engineers must adopt the manufacturing processes to include via fill and via plugging technology. I will dive into details of these processes over the next few editions of "Trouble in Your Tank." However, this particular column will focus on the need for via filling and some of the methods used to carry out the process.

#### Why Fill Vias?

Microvias, buried vias, and plated throughholes are filled with conductive or non-conductive materials for a number of reasons:

- Improved reliability (avoidance of trapped air or liquids)

- Improved planarity of multilayer structures (for more reliable surface mount or improved photolithography)

- Higher interconnect density (e.g., via-inpad vs. dog bone designs, Figure 1)

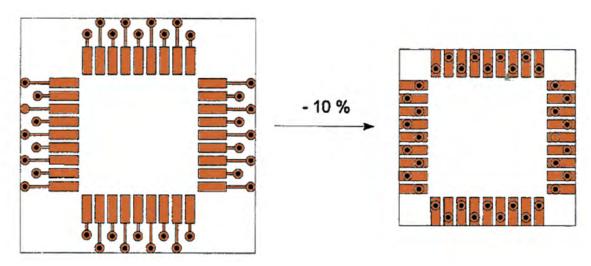

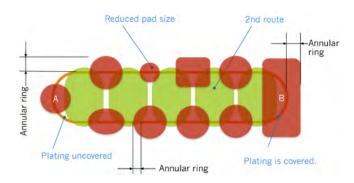

Figure 1: Via-in-pad versus dog bone design.

## LAMINATION SYSTEMS FOR PRINTED CIRCUIT BOARDS

STATE-OF-THE-ART SOLUTIONS FOR THE PCB INDUSTRY INCORPORATING THE LATEST TECHNOLOGY.

## INNOVATIVE POWER **4U**

Contact: Kurt Palmer 714-379-5090

burkleamerica.com

- Better thermal management

- Density, density, density

- Increased I/O number for packaging applications

- Minimized signal delays and to avoid defects associated with electromigration

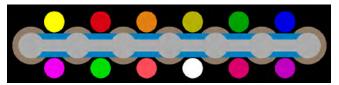

- Enables stacked microvia structures (often seen in smartphones' board technology, Figure 2)

Via-in-pad reduces the footprint as well as increases the density. This design concept places the via directly below the component contacts and reduces the footprint when compared to fan-out. When via-in-pad is used in a design, there will be the call-out for via filling or plugging process (more on the process options for via filling in a future column). Filling the via that is in the pad will improve the bond strength of the component when mounted over the filled via (Figure 2).

The concern with the issue shown in Figure 2 is that air inclusions during the lamination process may reduce long-term reliability. An additional concern with air inclusions is that, in effect, air is an insulator. Thus, air reduces both electrical and thermal conductance. While it is acceptable to endure very small voids in the via simply due to processing and material

Figure 2: Component mounted on unfilled vias (note the air pockets).

properties, it is desirable to minimize air voids through material property selection, via plugging techniques, and equipment designs <sup>[1]</sup>.

In the next few columns, I will present overviews of the different via fill technologies available. Meanwhile, one must first understand the definitions used for via fill and/or via plugging. While this distinction may seem trivial, it must nonetheless be clearly communicated between the board supplier and end user (as agreed between user and supplier, or AABUS).

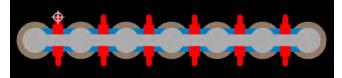

Figure 3 shows a schematic of an HDI structure containing through-holes, blind and buried vias, and microvias. Via hole filling is used for

Figure 3: HDI structure. (Source: Happy Holden)

the non-planar filling of plated through-holes. Via hole plugging is synonymous with the planarization of blind and buried vias as well as through-holes. Via hole plugging is applicable to HDI and microvia designs. Brushing (or planarization) is required to remove the excess material and create the flat surface. This technique is described in previously published papers <sup>[1 &</sup> <sup>2]</sup>. And there are some applications where the vias will be filled by a copper electroplating process commonly known as superfilling.

Superfilling or bottom-up filling of vias requires specialized plating processes, process controls, and plating cell set-up. This will also be the subject of a future column.

For the circuit board designer, the goal is to construct an architecture with flexible designs to ensure higher I/O densities as well as lower costs and greater performance. As Figure 3 depicts, there are four common via architectures for HDI:

- 1. Drill sequential lamination

- 2. Staggered sequential microvia build-up

- 3. Co-laminated any layer via stack microvia build-up

- 4. Stacked sequential microvia build-up

Yield issues are more difficult to pin down because they depend on a number of variables and are largely statistically driven (i.e., the greater the occurrence of a certain configuration will influence yields). Regardless, the four types of structures are used in HDI fabrication based on design constraints and routing density. **PCB007**

#### References

1. K. Andra, "Hole Plugging Technology for Multilayers and HDI Packages," EPC PCB Convention, 1999.

2. S. Kramer and M. Suppa, "Via Hole Filling and Plugging: Trends, Possibilities, and Limitations for Conventional and SBU-type Fillers," IPC Printed Circuit Expo 2001.

Michael Carano is VP of technology and business development for RBP Chemical Technology. To read past columns or contact Carano, click here.

## New Filter Enhances Robot Vision on 6D Pose Estimation

A recent study was conducted by researchers at the University of Illinois at Urbana-Champaign, NVIDIA, the University of Washington, and Stanford University on 6D object pose estimation to develop a filter to give robots greater spatial per-

ception so that they can manipulate objects and navigate through space more accurately.

While 3D pose provides location information on X, Y, and Z axes, 6D pose gives a much more complete picture. "Much like describing an airplane in flight, the robot also needs to know the three dimensions of the object's orientation—its yaw, pitch, and roll," said Xinke Deng, a doctoral student studying with Timothy Bretl, an associate professor in the Department of Aerospace Engineering at the U of I.

Deng explained that the work was done to improve computer vision. He and his colleagues developed a filter to help robots analyze spatial data. The filter looks at each particle, or piece of image information collected by cameras aimed at an object, to help reduce judgment errors.

The study uses 6D object pose tracking in the Rao-Blackwellized particle filtering framework where the 3D rotation and the 3D translation of an object are separated. This allows the researchers' approach, called PoseRBPF, to efficiently estimate the 3D translation of an object along with the full distribution over the 3D rotation. As a result, PoseRBPF can track objects with arbitrary symmetries while still maintaining adequate posterior distributions.

(Source: University of Illinois)

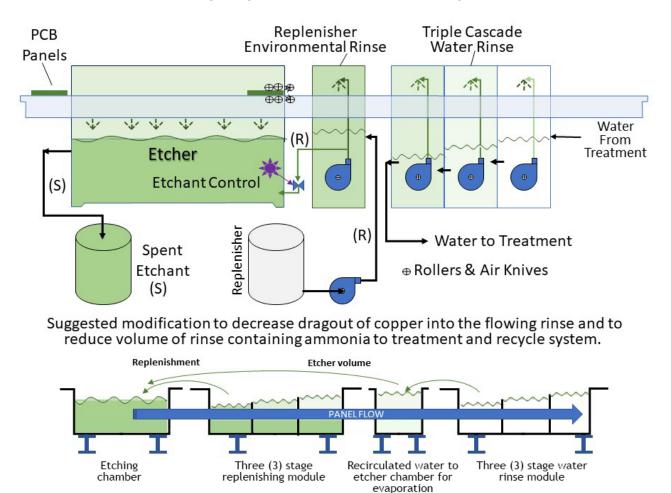

## Pollution Prevention Techniques: Rinse Water Reduction

### Article by Peter Moleux with contributions from Happy Holden