# APRIL 2021

$\infty \propto$

Welcome to SIMULATION CITY

# Master the art of keeping cool!

Learn how to beat the heat in your designs with techniques and methods from a fabricator's perspective.

DOWNLOAD NOW 🛃

Lively and insightful discussions from industry experts. Watch now!

App Notes and Fab Notes

Process Ionic Contamination Test (PICT) Standard

Achieving Operational Excellence in Electronics Manufacturing

Use of IMS Thermal Materials in Multilayer Stackups

## **APRIL 2021 • FEATURE CONTENTS**

# **DESIGNOUT** MAGAZINE The Simulation Issue

When we started speaking with SI experts for this issue, we were surprised to find that there were several schools of thought regarding simulation. Should you try to get by without simulating your design and only call a third-party consultant when it's almost too late? Should your company invest in a simulation tool, which also means hiring someone with years of experience to operate it? Or should you eliminate the need for simulation from the start by managing your electromagnetic fields properly? This month we asked some of the industry's premier experts on simulation to weigh in on this critical topic.

### **FEATURES**

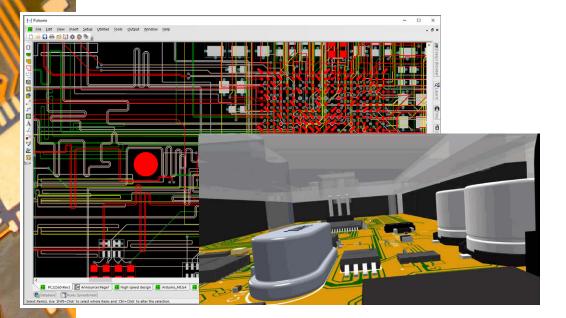

12 Barry Olney's High-Speed Simulation Primer Interview with Barry Olney

- 22 Bridging the Simulation Tool Divide Interview with Todd Westerhoff

- 34 Alternatives to Simulation by Dan Beeker

52 Why We Simulate by Bill Hargin

## FEATURE COLUMNS

- 60 Using Simulation to Assist With PCB Design by John Coonrod

- 80 Simulation Stackup and Signal Integrity by Martyn Gaudion

4 DESIGNO07 MAGAZINE I APRIL 2021

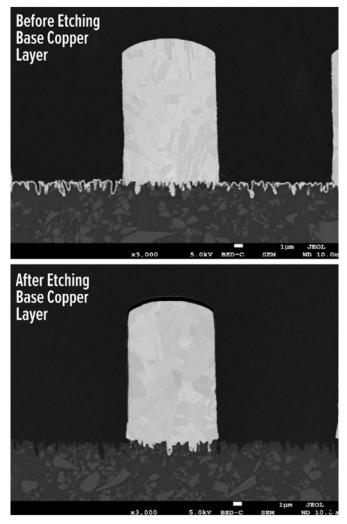

## Hmm, what is the difference between base and finished copper weights?

PCBs are complex products which demand a significant amount of time, knowledge and effort to become reliable. As it should be, because they are used in products that we all rely on in our daily life. And we expect them to work. But how do they become reliable? And what determines reliability? Is it the copper thickness, or the IPC Class that decides?

Every day we get questions like those. And we love it. We have more than 490 PCB experts on 3 continents speaking 19 languages at your service. **Regardless where you are or whenever you have a question**, contact us!

What's your PCB question? www.ncabgroup.com/PCBquestion

#### Reliable answers. Reliable PCBs.

## **APRIL 2021 • ADDITIONAL CONTENTS**

# **DI**

## **SHORTS**

- World's Most Powerful Modular Robot 43

- 51 **SolAero Technologies Powers OneWeb's Satellite Constellation**

- Linde, Bluefors to Develop Cryogenic 69 **Cooling Solutions for Large-scale Quantum Computing Technology**

- **SEMI** Applauds Initiatives to Bolster 75 Semiconductor Manufacturing, **Research in American Jobs Plan**

- 91 Sushi-like Rolled 2D Heterostructures May Lead to New Miniaturized Electronics

#### DEPARTMENTS 117 **Career Opportunities**

- **178** Educational Resource Center

- 129 **Advertiser Index & Masthead**

## HIGHLIGHTS

70 MilAero007

6 DESIGNO07 MAGAZINE | APRIL 2021

## **INTERVIEWS**

**Jan Pedersen: Getting Into** 40 **Ultra-HDI With IPC Committees** Interview with Jan Pedersen

**PCEA Expands in its Sophomore Year** 76 Interview with Scott McCurdy and Tomas Chester

#### **COLUMNS**

**A Simulating Conversation** 10 by Andy Shaughnessy

**Growth and Trends** 30 in the Thermal **Management Market** by Jade Bridges

- 44 Friends and Enemies in Power Distribution by Istvan Novak

- **Embedding Resistor** 64 **Elements**. Part 1 by Vern Solberg

- The Power Behind the (PCB) Throne— 72 **Power Supply Design Tips** by Matt Stevenson

- **Back-to-Back Chapter** 86 **Meetings and More** by Kelly Dack

- 92 Additive Electronics— **Next Generation PCB Capabilities** by Tara Dunn

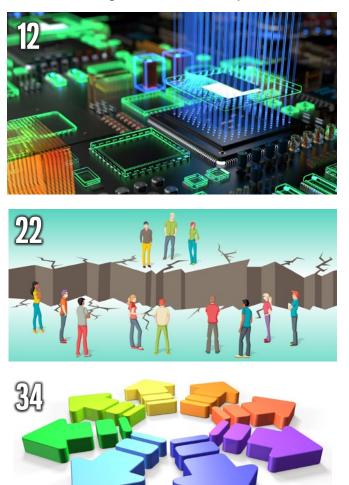

## No More Stackup Issues

#### With Z-planner Enterprise

It's essential to get your PCB stackup design correct to minimize schedule and cost risks to your project.

Z-planner Enterprise helps you design first-time optimized stackups that meet your specs and budget, plus you can map your design to your supplier's available materials and process capabilities. With the digital twin software provided by Siemens, you can get your designs right the first time.

> Watch webinar

siemens.com/software

### APRIL 2021 • CONTENTS

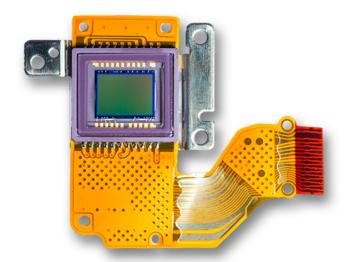

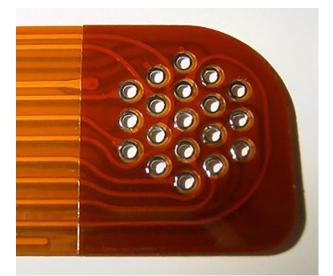

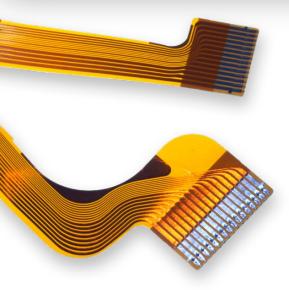

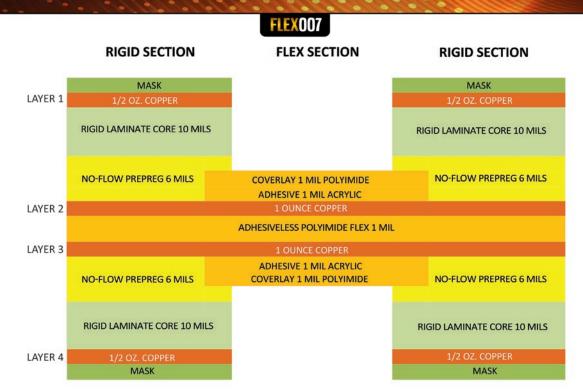

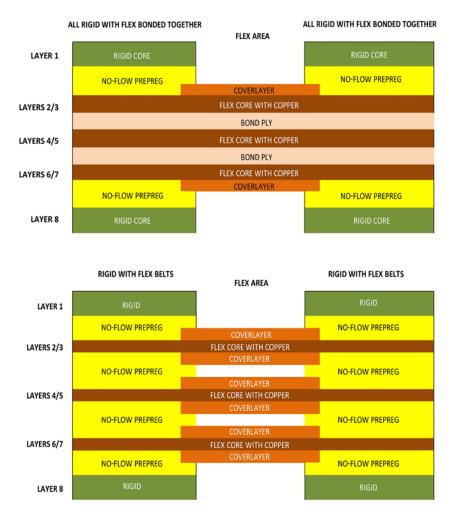

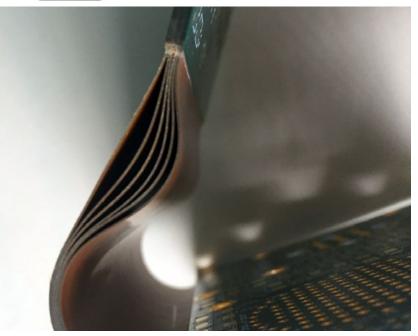

There are a variety of ways to terminate and connect a flexible circuit to a rigid board. But the stress on the flex circuit must be considered to avoid broken connections, and many flex connectors come with long lead times. This month, we look at some of the best techniques for terminating flexible circuits. One tip: Work out your connection strategy well in advance of beginning the design process.

#### **FLEX007 ARTICLE**

**106 Book Excerpt:** *The Printed Circuit Designer's Guide to...Flex and Rigid-Flex Fundamentals*

> **Chapter 2: Designing Flex Circuits for First-Pass Success** by Dave Lackey and Anaya Vardya

# Rexard Rigid-flex Fundamentals

#### **FLEX007 COLUMN**

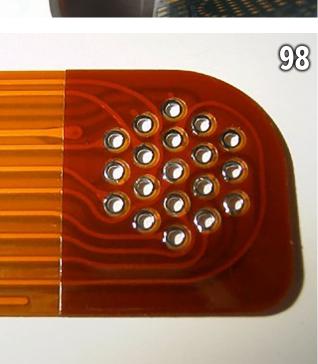

98 Termination of Flex Circuits by John Talbot

#### HIGHLIGHTS

**104** Flex007

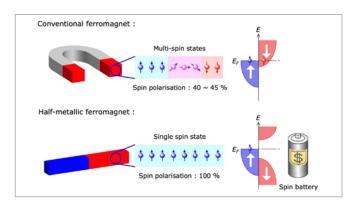

## **102** FLEX007 SHORT Putting a Spin on Heusler Alloys

## PREMIER GLOBAL SUPPLIER of **FLEXIBLE CIRCUITS**

## FLEXIBLE CIRCUITS | EMS/ASSEMBLY | CONTRACT MANUFACTURING

Superior design consultation & support Flexible Circuits Rigid Flex Flexible Heaters Flex/Rigid Flex Assemblies Membrane Switches Plastic Moldings Specialized EMS/Assembly Product Module to Complete Box Builds

## EXPLORE the POSSIBILITIES!

nol

a

Flexible Circuit Technologies 9850 51st Ave. N. | Plymouth, MN 55442 www.flexiblecircuit.com | +1-763-545-3333

# **A Simulating Conversation**

## **The Shaughnessy Report**

by Andy Shaughnessy, I-CONNECT007

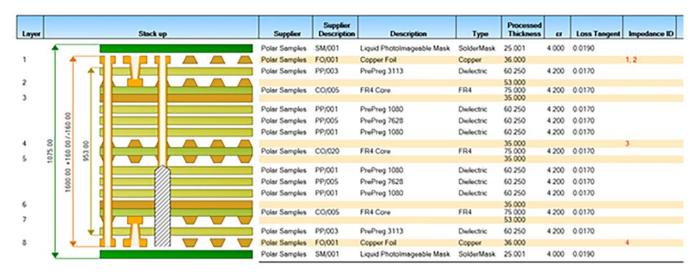

Simulation tools come in handy, and not just when you're designing a high-speed PCB. They're also a great conversation starter at a trade show. I'm talking about the live kind of trade show with a group of PCB designers and design engineers standing around a coffee break table eating stale conference bagels. (My kingdom for a stale conference bagel!)

Yes, simulation tools rank right up there with design data standards and China in terms of starting a conversation—or an argument—at a conference.

Here's how it usually works. I'll ask, "How many of you primarily work on high-speed designs?" Typically, it's a solid majority. How many of you are designing boards that are not high-speed?

Then I'll ask, "How many of you use simulation?" Out of 15 designers, maybe three hands will go up, and the whole group will chuckle knowingly. So, I'll follow up with, "Why don't you use simulation?" Answers often range from "It's really expensive" to "We just hope for the best" and "Don't get me started. It's complicated."

Apparently, it is complicated.

Then there are the simulation tools themselves, which are expensive and infamous for their steep learning curves. You can't park a recent EE grad in front of an enterprise-level simulation tool and expect greatness. As Barry Olney points out in his feature interview this month, even today's entry-level simulation tools are not simple to use and require the user to have a solid signal integrity background to get good results.

All of this sounds like the makings of a perfect storm. If the tools are expensive and hard to use, maybe you can get by without them, right?

When we surveyed designers and design engineers about their biggest challenges, sim-

ulation was a popular answer. Some respondents said that their design teams didn't fully understand how to operate simulation tools, while others faulted their company for not using simulation at all or waiting until the design was far behind schedule before sending the job to a third-party SI consultant. Comments included, "Management always budgets for re-spins" and "Time-to-market stresses won't allow simulation." Of course, if you fail EMI, your time to market is a moot point.

When we started speaking with SI experts for this issue, we were surprised to find that there were several schools of thought regarding simulation. Should you try to get by without simulating your design and only call a third-party consultant when it's almost too late? Or should your company invest in a simulation tool, which also means hiring someone with years of experience to operate it?

Plus, there is another viewpoint put forward by Dan Beeker: If you design your board correctly from the start and manage your electromagnetic fields properly, you may be able to eliminate the need for simulation altogether. Is your company already practicing this approach?

So, this month we asked some of the industry's premier experts on simulation to weigh in on the topic. First, we have an interview with Barry Olney of iCD, who lays out when and why engineers need to use simulation, what they need to measure, and why it takes years to master most simulation tools. Then, we have a conversation with Todd Westerhoff of Siemens EDA that covers simulation from the EDA tool company viewpoint, including some of the reasons why some companies ignore simulation, often until the 11<sup>th</sup> hour of a complex design.

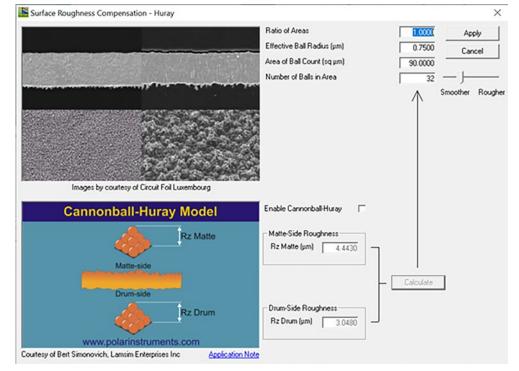

Next, Martyn Gaudion of Polar Instruments discusses the simulation of stackups, and why results are only as good as the source data. Bill Hargin of Z-zero takes a philosophical approach, beginning with a question he asks conference attendees: "Why do we simulate designs?" Dan Beeker of NXP Semiconductors explains how engineers can avoid using simulation entirely by managing EM fields correctly and focusing on the spaces—not the traces. And John Coonrod of Rogers Corporation discusses how he uses different simulation tools for different tasks, and he compares and contrasts 2D and 3D field solvers.

Do you have a great story about simulation successful or otherwise—that you'd like to share? Shoot us an email at editorial@iconnect007.com. We're always looking for good content.

See you next month! **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 20 years. He can be reached by clicking here.

## **Barry Olney's High-Speed Simulation Primer**

#### Feature Interview by the I-Connect007 Editorial Team

The I-Connect007 editorial team recently spoke with Barry Olney of iCD about simulation. Barry, a columnist for *Design007 Magazine*, explains why simulation tools can have such a steep learning curve, and why many design engineers are still not using simulation on complex high-speed designs.

Barry also highlights common mistakes that design engineers make using simulation tools, and he offers a variety of tips and techniques for anyone dealing with simulation challenges. Among them: Don't trust reference designs and datasheets.

**Andy Shaughnessy:** What are some of the biggest problems in simulation? In our surveys, engineers say that they have trouble doing simulation and analysis. What is so tough about it?

**Barry Olney:** I think the biggest problem, Andy, is time, and that's the same with PCB design in general. The PCB design is the last process in

the design flow, and when I get a job for a board layout, it's already behind schedule. I've never ever had a job where it was on schedule and everything was running smoothly. So, you're pushed for time during the whole process, and to add simulation on top of that, that pushes it back another week or so. Management is reluctant to do it because they think, "Well, it may work and then we can get it through just a little bit behind schedule, but if we leave it another week then it delays things even further." It seems they don't have time to do it right the first time, but they've got the time for a re-spin.

A lot of engineering managers actually schedule in a re-spin because they believe they need at least two iterations before they get a working product. So, time is the biggest factor. That's why they generally tend to skip simulation. There's also the learning curve associated with the high-end tools that requires experience not just with the tools, but with high-speed design rules. Sourcing IBIS models is another big issue. Maybe you can't find the model, so you have to compromise. IC vendors are now supplying most IBIS models, but for FPGAs, NORTH AMERICA'S LEADER IN HI-TECH QUICK TURN

# ELEVATE YOUR BUSINESS WITH

\$10 MILLION IN RECENT TECHNOLOGY CAPEX INVESTMENTS NIST 800-171 COMPLIANT CYBERSECURITY PROCESSES 250,000 SQUARE FEET SUPPORTING ALL TECHNOLOGIES 4 STATE-OF-THE-ART NORTH AMERICAN FACILITIES

VIEW OUR QUICK TURN VIDEO NOW

www.summit-pcb.com

in particular, if you get the default IBIS model from the vendor's website, it has a default pin assignment, but once the EE places and routes the actual FPGA chip, you need to redefine the pin assignments for each signal.

Now, the pin assignment of the FPGA that someone designs isn't the same as the one on the IBIS model, and that's where it all goes haywire. You think, "That simulation is simple. You just have to import the IBIS models into the transmission line model and click Go." That should happen, but, it doesn't. Where you don't have pin assignments matching, you have to manually select the required FPGA sub-models from the thousands of pins with 50 or so sub-models. And these have all got cryptic names that are different for each IC vendor. So, you actually have to find the model or driver model that matches the transmission line that you're trying to simulate. Or maybe you cannot find the model at all. Good luck sourcing a connector model. So, again, this all takes time. It took me years to figure out how to do it properly, quickly, and efficiently.

The other thing is the cost of ownership, of course. The high-end simulation tools are expensive, as you know, and are beyond the budget of the average punter. So, it's better to outsource simulation. From a cost point of view, it's not all that expensive. Alternatively, EDA vendors have professional packages that include basic simulation tools. OrCAD has Signal Explorer, that I am now using; PADS has BoardSim EXT, a cut-down version of HyperLynx; and Zuken has tools like Lightning in their CR-5000. These are all entry level simulation tools, but they still require a lot of background knowledge to get them up and running. They are not that simple to use.

**Shaughnessy:** Do you basically have to be an SI or PI engineer to use simulation tools? Are there any simpler tools that fall under the simulation umbrella that, say, a PCB designer could use?

Barry Olney

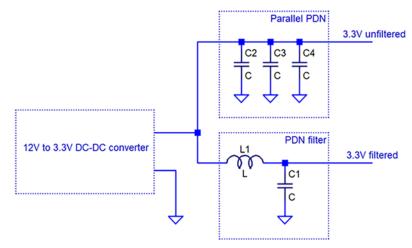

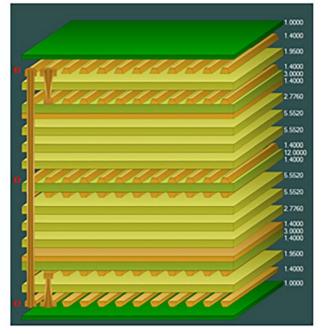

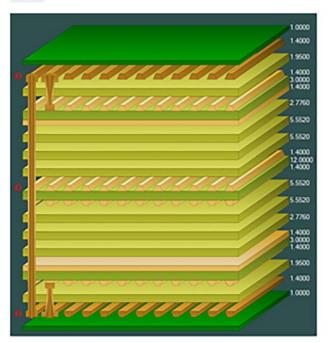

**Olney:** Simulation tools encompass many subtools. For instance, stackup planning and PDN planning is all part of simulation and that can certainly be done by the average PCB designer. The stackup needs to be assigned before you even start placing a chip on the board. You need to define the differential pairs and accommodate different technologies on the same layers of the PCB. You may have a 50-ohm digital signal with 100-ohm differential pair. You may have a DDR3, which has 40-ohm single ended and 80-ohm differential impedance. You may have a USB that's 90 ohms. All these have to work on one substrate, so you need to account for all these different technologies and work out the impedance for all those before you even start your design. PCB designers can certainly do that. It's not difficult. It's pretty straightforward.

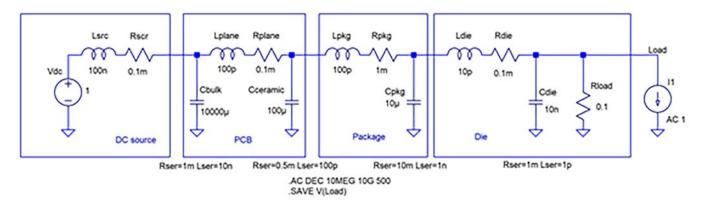

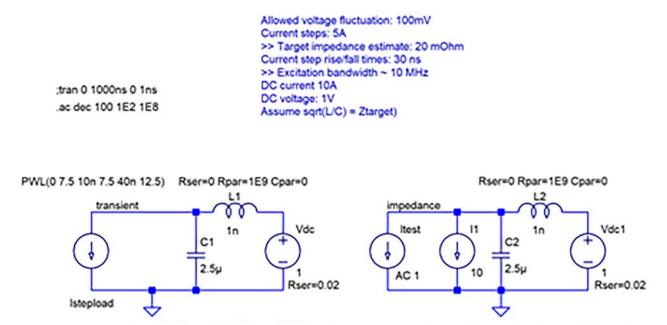

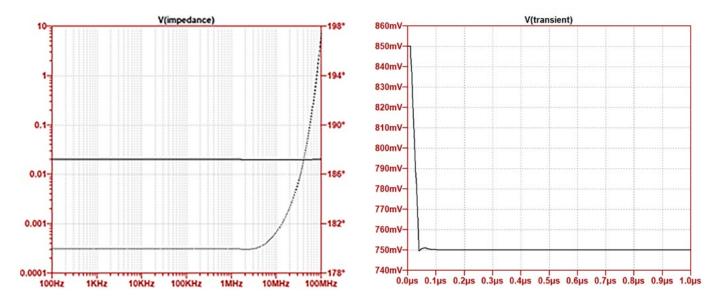

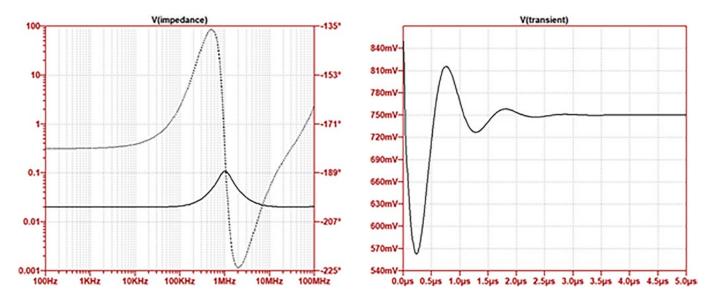

PDN planning can also be done by the PCB designer. The optimization of the PDN is a trial-and-error process that needs to be done in conjunction with the stackup materials, planar capacitance, and decoupling, to fully

exploit all avenues. The idea is to lower the AC impedance of the planes.

**Shaughnessy:** Barry, what's the cutoff? How should a company know when it's time to either invest in a simulation tool or just start farming out simulation? Do they look at it by the speed or the rise and fall rates, edge rates, or if it's serial links? Who would you recommend?

**Olney:** When it's too close for comfort, basically it's time to do signal integrity analysis. There's two ways of looking at it. There's the old, lumped-element method working in the time domain. That's static timing or the relationship between clock, data, address, and command signals. But what you must appreciate is that that static timing rides on an electromagnetic carrier weight. You have your static timing, which is critical, that rides on this wave of electromagnetic energy through the transmission line. We are used to visualizing the static waveforms on the oscilloscope in the time domain, but we also need to think in the frequency domain. It's a different world working in the frequency domain compared to the time domain. The frequency domain is particularly suited to analyzing the PDN.

This electromagnetic field that transports the static signals can also vary depending on whether it's running on a microstrip or a stripline configuration. If it's on the outer microstrip layer, because there's a mixture of solder mask and air in the dielectric, it tends to speed up the signal. It reduces the dielectric constant because the velocity of propagation is the speed of light divided by the square root of the dielectric constant. If you have a lower dielectric constant, then you have a faster speed. So, you must take into account the actual static timing of the devices, their relationship between the clock and the data and address, plus the timing of the propagating signal through the transmission lines.

**Shaughnessy:** When you have customers come to you, what are some of the typical jobs where they should have done a simulation and they didn't?

**Olney:** Generally, memory analysis. DDR is new territory to a lot of designers. They want to feel confident in what they've done and make sure they haven't made a mistake. That's one reason why people get simulation done, and the other, of course, is they have a board that doesn't work, they've been trying to fix it and they need help. That's when they're desperate, and it shouldn't come to that; that's plan B. Simulation should be done up front, as I've mentioned before, you need to do it before you even start placing a chip on the board.

**Happy Holden:** Are there situations where the board might work but you fail FCC? What other external things can you fail even though you connected the point, and it seems that the board works?

**Olney:** Yes, that happens a lot with reference designs. A reference design is done by smart engineers who design chips, and they know how to do a basic PCB layout, but in general they're not highly experienced PCB designers, so they don't know a lot about design for manufacturability. These new reference designs work great in the lab with a few wires hanging off here and there. Great, we've got it working. They make the reference design available, and everyone copies it thinking it's a golden board. But if you were to temperature cycle the board for the equivalent of 10 years, there are reliability issues. So that's generally what happens—intermittent problems in the field.

**Shaughnessy:** Do you find datasheets to be helpful?

**Olney:** I always say to assume the datasheets are wrong, especially libraries of physical components because you look at a mechanical draw-

ing and there's always one number on there that just doesn't fit, and you've got to work it all out. You can generally go back to the actual physical component and measure it. There's always something wrong with the datasheet.

**Shaughnessy:** I remember the big three EDA companies were talking about having simulation tools that would run concurrent with the design, like they would be running during schematic and all through. Is that how it is now or is it something that is right at the very end?

**Olney:** Ideally you need to do that, yes. You need to simulate the schematic, which you can do. You can create freeform schematic models and then add an estimate of the lengths of the transmission lines. For example, for memory you may say, "I have two and a half inches here. So, I'll put a two-and-a-half-inch,  $50\Omega$ , transmission line, attach an IBIS model at either end and see how it goes." That's really good for building up the maximum length you have to play with because before you do the placement you need to know the maximum timing you can have on a chip. If you place the chips too close together it's difficult to route, and if they are too far apart then it may mess up your transmission lines with long delays and too many reflections.

So ideally you need to work out the placement before you put the chip on the board, and that also helps with your routing topology. You may want to do flyby topology-that's how you generally do DDR3 and DDR4-but there's no need to do a flyby if you've only got a couple of memory chips. You can still do a T-topology route, which means branching out with equal delay into each chip. All the professional EDA tools now have a way of extracting the topology, so once you have routed a particular section you can extract the topology of that from the PCB, so you get the physical transmission line. That includes whether it's running on microstrip or asymmetric stripline, for example. It builds the actual physical structure of the PCB, including layer transitions (vias), into

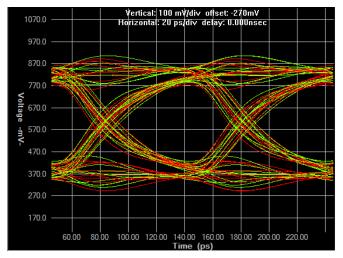

Much of high-speed simulation is centered on achieving a nice eye diagram.

the simulation model. Then you can virtually simulate the board itself, so that's the final process—making sure all the timing is right on the physical simulation.

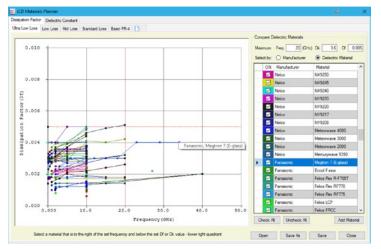

**Holden:** Does anybody publish or sell a good dielectric material library?

**Olney:** I do (laughs). Actually, our stackup planner has 35,330 individual materials at different frequencies. There is a choice of over 700 series of rigid and flexible dielectric materials from over 60 manufacturers. There is every material you would ever need. If you can't find a new material, I'll add it free of charge. It's very comprehensive.

**Shaughnessy:** What good sources of information on simulation analysis are out there? If someone is new to the industry, what would you recommend to them as far as getting some more information?

**Olney:** Well, I think reading your magazine, Andy, is a good start, and other industry magazines. The SI Forum is a really good source of information with many experts on there that can answer your questions, as is attending any of the technical seminars that Rick Hartley and people like him run. They are a good start. I

## SIGRITY AURORA ANALYSIS

Resolve PI and SI issues at any stage of your design with Sigrity Aurora. Real-time, overlaid simulation results allow you to quickly analyze, identify issues, and verify fixes from within a shared PCB design and analysis platform.

Experience true, electrically-aware design from start to finish with best-in-class Sigrity and Allegro engines.

started off attending conferences and technical sessions. Happy's "Design for Manufacturability" was probably one of my first back in 1990. You can learn about the engineering process, but design for manufacturability is very important, and it's not taught in universities. There are a few courses on signal integrity that are targeted at EEs but not so much PCB designers. I developed the "Advanced Design for SMT" course for the Australian Electronics Development Centre back in 1994 to teach high-speed design techniques.

**Holden:** I guess we should qualify that a lot of what we're talking about in terms of problems apply to analog and digital designers, but if people are involved in RF design and doing it correctly then they have learned a lot of these things early on. It's just that the percentage who are really good RF designers is so small.

**Olney:** RF and microwave design is a different world altogether; the circuits are very high frequency with fast rise time and short wavelengths, so you need to be very careful. Every stub is an antenna. That's why coplanar waveguides are typically used for RF, because they tend to stabilize the signal. For a microstrip signal, for instance, you've got coplanar waveguides with ground pours on either side of the signal which tends to dampen the radiation.

**Shaughnessy:** A lot of designers and engineers agree that simulation is a great idea, but many of them don't use it. Why don't more people use simulation?

**Olney:** I'm sure it's mainly to conserve time. Managers always strive to reduce their design cycle. But simulation isn't that expensive or time consuming if you outsource it. For instance, I can analyze an average complex board for about US\$5,000 and find the problem. If I were a manager and I had a choice of a small investment in analysis or taking the risk of a re-spin, I know which I'd choose. It's a nobrainer as it verifies that the product will perform reliably!

**Dan Feinberg:** One of the things that you just raised and Happy just mentioned is that people often look at price, but it's really cost, and they're different.

**Olney:** Absolutely. The cost of a re-spin is a lot more than the price of the tools or outsourcing analysis. It's not just engineering time you are wasting, but time to market and lost opportunity which can be extremely costly.

**Shaughnessy:** Lee Ritchey says a lot of these conflicts stem from a managerial viewpoint versus the engineering viewpoint. The manager thinks, "Great, the design was done quickly," even though there may be a costly re-spin down the road, because for now, the EE can get on to another project.

**Olney:** That's right, you'll always have conflict. Engineering and management require different skill sets. The manager is responsible for getting the project completed on schedule and to budget. And, he has to look good to his boss. If he schedules a re-spin, then it is expected. It's in the timeline. Whereas the engineer or PCB designer is more interested in the completion of their work and learning new techniques to improve their skills.

Holden: Is PCB design growing in Australia?

**Olney:** I guess I am a little out of touch with the Australian electronics industry as I mainly do business overseas now. We have small groups of designers, but there is not a large electronics industry except for defense contractors. It was always difficult to sell VeriBest PCB and Mentor (Siemens) tools in Australia because it's the home of Altium, of course. Everyone uses Altium and going against tradition is very difficult. I guess you could say that the Altium Designer's market is growing. There isn't much

of a market for simulation tools either. In fact, in the past, anyone who did well ended up going to the U.S., so you lose a lot of talent when a company becomes successful; it just disappears offshore.

**Holden:** Where do your customers come from?

**Olney:** Lately, the U.S. Probably 70% of my customer base is in the U.S., 25% in Europe, and 5% from other countries.

**Shaughnessy:** Do you have any recommendations for somebody dealing with simulation challenges right now? Any tips?

**Olney:** Sure. The biggest thing is forgetting what you learned at university. Circuit theory is all DC, but when you get into the frequency domain, with high frequency, fast rise time signals, and a distributed system, you need to think in the way of the electromagnetic fields, coupling, and radiation. It's a different world altogether. You really need to educate yourself before you can become a good high-speed designer. The other point I'd like to make is that simulation tools don't complete the analysis toolset. My eyeball is just as good as any signal integrity tool. That's because I have (embedded in my skull) 30 or 40 years of IPC design rules, design for manufacturability, and SI and PI requirements, so I can see a lot of issues before I really need to simulate. Just looking at the topology of the routing, for instance, gives me an idea of whether a design will perform to expectations. On the other hand, simulation gives you another set of eyes and allows you to visualize other issues.

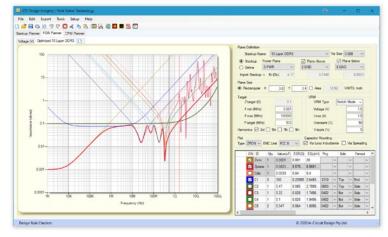

When I do an analysis, I think outside the square. I drill down through the board; I do a teardown of the substrate. First, I look at the impedance and different technologies that must run on each layer, the materials used, and at the minimum cost, of course. It must provide adequate performance, but it doesn't have to be the best material, and it also has

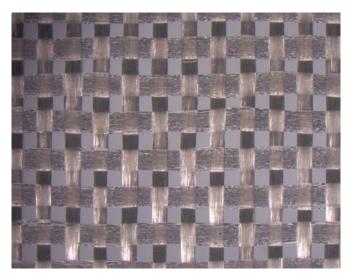

An In-Circuit Design field solver simulates a DDR3 stackup.

to be stocked by your fab shop. So, you must choose the right material for the right job.

These days, one of the largest problems is the amount of power supplies you have on a board. I think the last design I did had 35 power supplies.

Some believe, "Routing is simple. You just route between two planes and keep the critical signals isolated, etc." But until you get in amongst it (as a PCB designer, which I am) you come across the real problems of space. You just don't have the space to put in everything, while working out where these 35 copper pours go, and not interfering with anything else is a major problem in board layout. If you have a trace that crosses from one power plane to another, you are creating return path discontinuities and it can cause untold problems with EMI.

So, you really need to plan how you're going to place these power supplies to get the most effective route. If you can't route a board it may not be because you don't have enough layers. People often say to me, "How do you know when you've got enough layers? Is eight layers enough, or do I need 12 layers?" After a while you get a feel for it. But a good way to test it is just to let your autorouter go loose, and if you don't get 85% completion, then you've got something wrong. If the board is difficult to route, then it may be because of placement. You need to open channels for the router.

A materials planner tool allows the user to compare Df and Dk of various materials.

One of the things I talked about was time. A lot of people start designs when they are not ready for layout. They say, "We started the design, and we'll give you the main processor, the memory, and the power supplies," for instance. You start with these, move things around, and change them from one side of board to the other. Spin them and rotate them and whatever to get the best placement to prevent the rat's nest from crossing over, then route that section. Eventually the EE finishes the schematic, and you add all the other chips. "But the processor would have been better on the other side of the board." Turn it the other way around and all the signals would not be going through the center of the board from one side to the other. So, my recommendation is to never start a board until the schematic has been finished, approved, and it's ready to go.

The other thing I do when I'm analyzing a design is to look at the PDN, which is very important from a stability point of view. The key points for stability in the design are stackup impedance and the AC impedance in the PDN. Adding planar capacitance by using very closely coupled power/ground planes pairs, positioned close, in the stack, to the top and bottom ICs, has a dramatic effect on reducing the AC impedance. This is where the stackup configuration needs to be adjusted in conjunction with the PDN plot. Minimizing the reflections on high-speed signals is another thing. You may have a driver, and typically the source impedance of the driver is between about 10–30 ohms. But, you need to have a transmission line of say 50–60 ohms. Now, that won't match to a driver of 10–30 ohms. In high-speed design you need to have either a series terminator or a parallel terminator at the end of a long line. Parallel terminations simple match the transmission line impedance of  $50\Omega$ . But a series termination must be calculated. The iCD Termination Planner, for instance, extracts the attributes required to determine the source impedance of the

driver from an IBIS models IV curves. Then the series termination resistance is calculated, based on a distributed system and load, to match the transmission line for the selected layer in the stackup. In a typical digital design, you've only got the rise time to worry about, but with DDR you've got the data being clocked from both the rising and falling edges of the signal. So, you need to also look at the falling edge of the waveform, and that's quite a lot faster than the rising time of the device. This is due to the design of typical CMOS output drivers. For the same feature size transistor, an n transistor can turn on faster than a p transistor. So, the fall time is always faster than the rise time-which you need to consider.

Simple things like that will get your reflections under control. Now, reflections create a lot of crosstalk because if you have close coupling on the signals, which you normally do with tightly routed boards, you don't have a lot of room. You've got to route things close, and so you get coupling and crosstalk, which creates radiation. EMI is created from all these reflections. It's stabilizing the impedance and the power supply that stops these reflections and radiation allowing the product to pass EMC tests. All critical signals should be simulated. I don't actually simulate every signal within a bus. If you've got a huge bus with 128 bits, you're not going to simulate each one, but one from each byte lane is enough because they're all routed much the same. Pick the worst-case signals to simulate then the rest will be fine.

When you're routing the data group of signals, it should all be done on the one layer of the substrate. A lot of reference designs that I have seen have address lines and data lines routed on the outer microstrip layer and some on the inner stripline layers. As I mentioned before, that all impacts timing, because of the different velocity of propagation of the outer and inner layers. If you run the entire bus on one layer, then you're matching the timing automatically, so that saves a lot of simulation time and risk.

Crosstalk is very difficult to predict. When I do a teardown of the board, I look at every layer with respect to every other layer. I'll have a look at layer one, which may be a signal layer with respect to the layer two, which may be a ground, and look for any signals outside that ground plane, because once the signal leaves the plane area that increases its impedance, and it will radiate and cause problems.

When you get to stripline, you may have dual asymmetric stripline, and you will have two traces between the planes. You need to look at the planes with reference to each signal layer and see where the return paths will flow. We tend to route signals from one point to another from a driver to a receiver, but what you must understand is the return current will flow with high frequency directly underneath that signal trace, and if there's a split in the plane, or it has to change layers in some way, then you need to facilitate that.

If you have two ground reference planes, for instance, you can place a ground stitching via where the layer transition is. However, if the reference plane changes from ground to power, traditionally we use one decap across the planes to provide a return path for the current. If you have two different power supplies—for instance, a 5V and a 3V—and you have traces going across the split, you should put in a decoupling capacitor going from the 5V to ground and then from the 3V to ground. This stops the noise coupling between the two different power supplies that are going through ground rather than just from supply to supply.

There are a lot of things to look at about overlapping your signals. Broadside coupling is very, very difficult to spot because when we are routing we generally turn off the other layers or just dim them in the background. We are just looking at the one layer we are routing and pushing things around, and we don't understand or see what's on the other signal layer near it. In the stripline situation where you have broadside coupling, you have the width of the trace coupling to the width of the trace below, which is a lot more coupling area than you would have with an edge coupling because you only have the very thin edge of the trace with edge coupling. With broadside coupling, you have a wide trace coupling to another wide trace, and generally you've got a very thin dielectric—like a 3-mil—in between. That makes a beautiful coupling, maybe a good RF coupling, but it's not what you want to do in digital design. Also, be careful of broadside coupling on built-up microstrip layers.

**Shaughnessy:** It sounds like a lot of this comes down to following solid design and engineering practices, but also having the experience to know what to look for. You can't be a part-timer with simulation tools, I guess.

**Olney:** It's all about experience. Experience is the greatest teacher of all! That's why I say you can't just put a tool in front of an EE who's just out of college. They don't know what to do—it doesn't make sense to them. They don't understand the principles or concepts, and someone needs to give them direction in how to analyze high-speed designs quickly and efficiently.

**Shaughnessy:** This has been really great. Thanks for speaking with us.

**Olney:** Thank you. **DESIGN007**

## **Bridging the Simulation Tool Divide**

#### Feature Interview by the I-Connect007 Editorial Team

Todd Westerhoff of Siemens EDA recently spoke with the I-Connect007 Editorial Team about the divide between users of high-powered enterprise simulation tools and those who need a more practical tool for everyday use, and how Siemens is working to bridge the gap. Todd also shared his views on why so many engineers do not use simulation, as well as advice for engineers just getting started with simulation tools.

**Andy Shaughnessy:** Hi, Todd. This is our simulation issue, and we want to get your thoughts on some of the challenges in this area. What do you see right now? What's the biggest problem in simulation?

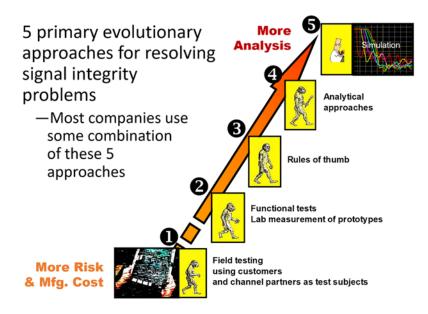

**Todd Westerhoff:** I think the biggest challenge is that there just aren't enough people simulating. There are a lot of people who are designing to rules of thumb, manufacturer guidelines, or getting somebody else to run analysis for them—but there aren't that many simulating themselves. I usually break simulation users into two broad groups: SI experts, who run simulations full time; and everyone else, who run simulations intermittently, if at all. The SI experts have the most advanced requirements and are also the smaller of the two groups.

The general assumption about simulation seems to be that it starts at the top—if we meet the analysis needs of the experts, knowledge and technology will trickle down over time to the broader audience. The problem is that, as an industry, we have too many designs in progress with too few experts to support all that activity. Simulation has two main purposes:

- 1. Providing a basis for making informed decisions about design trade-offs.

- 2. Validating a design before manufacture to reduce the risk of prototype spins.

How do we expect the majority of system designers to make decisions and reduce risk if they don't have data to back up those decisions?

Most of the simulation that we need to make design decisions and detect issues during layout doesn't require expert-level attention to

## Candor Circuit Boards

# Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

## www.candorind.com | (416) 736-6306

detail—the need is far more pedestrian. We're not servicing those needs when we focus primarily on the state of the art. SI tools have been around for 30 years now, and we still see the majority of people not simulating, so we need to consider doing something else.

**Shaughnessy:** Maybe they don't need a tool that you have to be an experienced signal integrity engineer to operate. Can a regular system designer or layout designer use the simulation tools we have today?

Todd Westerhoff

Westerhoff: Depending on the tools you talk about, yes and no. Let's go back to our classes of users. Experts are looking for advanced tools with state-of-the-art performance and capacity. Ease of use is a consideration but not critical, as experts can make pretty much anything work. They have deep SI knowledge and can improvise analytical methods when the situation calls for it. To your question, the tools used by full-time SI/PI engineers are typically not usable by mainstream designers, because the tools by themselves are not enough. You need an analytical methodology, or workflow, to apply the tools to a design and determine whether the design will work, and that process is typically complicated enough (and manual enough) to preclude use by someone who isn't performing analysis full-time.

And that's the rub: if we're not designing a 112-gigabit serial link or a loaded DDR5 interface, most of the issues we face during design and layout don't require the kind of accuracy that an expert is looking for. There are a lot of design issues you want to take off the table before you put a lot of effort into modeling and simulation. You can think of it this way: Experts typically simulate at the level of accuracy needed to "sign-off" a design for fabrica-

tion, but system designers are often just trying to assess the impact of a tradeoff on design margin. In those cases, a good answer now is preferable to a great answer later. You can think of that as "trade-off" analysis. It's less accurate, but faster to run and accessible to a wider audience. That's the kind of analysis that needs to be accessible to regular system or layout designers. We have some of those tools in place today, but the world clearly needs more.

**Shaughnessy:** Everyone agrees that it's rough going at first, trying to understand simulation without decades of experience. Where would a young EE start?

**Westerhoff:** Signal integrity is one of those fields where there seems to be a lot of tribal knowledge and a relative scarcity of basic training material for new users. DesignCon papers are great for advancing the state of the art, but they are often over the heads of people who don't do SI for a living (this stuff is complicated, after all).

What's the new engineer supposed to do? We seem to have basic material that's easy to understand but doesn't really help you make design decisions, and advanced material that gives you a mathematical formulation for how the physics work, but not enough in-between. There are people who can look at Maxwell's equations and understand how EM waves propagate, but I'm not one of them. It took me a long time to understand why RF structures are characterized the way they are, and how that applies to time-domain circuit analysis. I don't see enough material that explains physical phenomena at a practical, intuitive level and links to the types of design decisions that engineers need to make.

Let's take a step back: What's the most important question when I'm designing something?

#### Nolan Johnson: Does it work?

**Westerhoff:** Bingo! The details get complicated but the question is simple: Will our design work, and by how much? How much margin do I have available to make design trade-offs that reduce manufacturing cost, or whatever?

**Johnson:** Are you talking about something like digital simulation? Is the logic of my schematic going to behave the way I expect it to? Are you looking at the behavior of your schematic at a logical level?

**Westerhoff:** Great question, but I'm talking about something different. Logic simulation is about making sure my design creates the right logical 1's and 0's, that it has the correct logical function. That's a binary problem: it either works correctly or it doesn't. Signal integrity is about the analog behavior of digital signalswhether they achieve the right voltages at the right times to ensure that signals are received (sampled) correctly. That means we can have margin-the degree by which a signal's voltage exceeds a minimum voltage and timing needed for reliable operation. We want to have enough margin to be reliable but not so much that the design becomes cost-ineffective, since increasing margin tends to increase the cost of producing the design.

Often people will say, "Just take the vendor's reference design and copy it." That works, but with drawbacks, because reference designs tend to be conservative, for good reasons. One, they're the first board built for that particular IC, so nobody knows where they can cut the corners yet. Two, the IC vendor absolutely wants to prove the chip is reliable and they're not trying to manufacture the reference design in volume. So, what's cost-effective for a reference design may not be cost-effective for volume production. Three, what happens when a mistake gets made while copying the reference design? Signal integrity issues can be notoriously difficult to debug in the lab simply probing a marginal signal can be enough to change its behavior. What happens if you have a low-cost, high-volume consumer design that's failing intermittently in the lab?

Signal integrity issues can be notoriously difficult to debug in the lab simply probing a marginal signal can be enough to change its behavior.

**Shaughnessy:** How do you convince people to use simulation in the first place? At DesignCon, a moderator will ask who uses simulation, and three hands might go up. Is it that due to time to market?

**Westerhoff:** Let's start with why people simulate. I'll give you my list of five reasons why people get started with simulation.

1. There's no other path forward. When I'm designing a new chip with a new package, there are no pre-existing guidelines or rules. It might be a standardized interface, but the IC layout is new, and the package is new, so I know full well that everything won't just come together by itself. I'm going to have to model everything and prove that it works before anything gets built. That's how we designed ASICs in my past; we proved we had a working board-level solution before the chip is taped out.

2. People start simulating because they're having lab failures that affect project schedules and costs. I'm not talking about inconvenience; I'm talking about real impacts. One company we talked to was making small boards for consumer applications, but spending over \$150,000 a year on prototypes due to problems that were readily detectable with simulation. There was a clear argument for saving money, even with a tool purchase and the ramp-up cost of training a new user.

3. Costs and delays associated with outsourced analysis pile up to a breaking point. If I use someone else to do my SI analysis, that takes time and money—even if the SI consultant is internal. If I outsource enough work, it becomes a problem. It doesn't have to be about cost; if lots of people rely on the same SI consultant, they're all dependent on what other jobs the consultant has already committed to. Time is money.

4. Reference designs and rules of thumb run out of gas, and/or overdesigning drives up manufacturing costs to a breaking point. Commodity consumer products will be especially sensitive to something like this.

5. Organizations are proactively seeking to improve their design processes.

**Shaughnessy:** Wait a minute. You're saying that process improvement ranks last in terms of reasons why people start simulating?

**Westerhoff:** I am because I'm being practical. Companies don't make big investments to solve problems that aren't costing them a lot of money. They always have other things to worry about.

Simulation is a lot like having good habits: we all agree we should. We all agree that we should floss, eat more vegetables, and exercise more. The question is, how do you lower the barrier to helping someone get started and keeping the process going?

Here's a paradox: If most of what we talk about are the state-of-the-art problems in signal integrity, then we're making the barriers to entry greater, not lesser. We're experiencing an "expert crunch" already and focusing almost exclusively on technology makes it worse.

**Johnson:** The automotive press is similar: There's lot of coverage on the Corvette and it sells magazines, but when most readers go to the dealership, they buy a Toyota.

**Westerhoff:** So the question becomes, what does it take to make someone productive with SI and PI tools? I propose that there are three main components. The first is domain expertise. If you don't know what characteristic impedance is, I'm not going to show you what to do with a signal integrity tool, because you won't understand the problem to be solved. The sec-

So the question becomes, what does it take to make someone productive with SI and PI tools?

ond component is tool training, and that's actually the easy one. The third component goes back to our fundamental question: Will my design work? If I give you a simulation tool and you run a simulation, then what? How are you going to determine if the design passes or fails, and by how much? You need a complete analytical methodology for verifying your design's behavior against a spec to determine operating margin. That methodology will be protocolspecific, and sometimes component-specific.

So you need knowledge, you need tools, and you need an analytical methodology that maps to your interface's specific requirements. People who run SI simulations for a living will put the pieces together themselves, but system designers and layout designers need solutions that work right out of the box. That's what we're trying to do.

## STRIVE FOR EXCELLENCE www.emctw.com | EMC.INFS@mail.emctw.com

## Enable 800GbE Ethernet Speed with EM-892K and EM-892K2 Materials

## Industry's First Halogen-free Extreme Low Loss (ELL) Laminates

World's largest producer of environmentally-friendly advanced laminate materials

Key Material Features: EM-892K @70%RC: Dk: 2.84/ Df: 0.0017 @10GHz EM-892K2 @70%RC: Dk: 2.76/ Df: 0.0013 @10GHz with Cavity Resonator Method

Lead-Free Soldering Test: PASS LF-260°C/ 10X with 32L 0.6mm hole pitch

Anti-CAF Test: Pass 100V/ 85°C/ 85% RH with 32L 0.6mm hole pitch for 1K Hours

IST Test: Pass Room temperature to 150°C for 3K Cycles with 32L 0.6mm hole pitch

North American Master Distributor 1-800-909-8697 • www.technica.com **Shaughnessy:** What advice would you offer to someone just getting into simulation who already knows how to design a board?

**Westerhoff:** Personally, I try to listen to everything that Eric Bogatin and Scott McMorrow say, for different reasons. Eric is a phenomenal educator, and he has a gift for breaking complex topics down and communicating them. Every time I listen to Eric, even on a topic I think I know well, I learn something new. Scott has been state of the art for the 20 years I've known him and shows no signs of slowing down. Every time I talk to Scott, I learn what issues are coming at me in the future, whether it will be six months or two years from now.

It's important that users take the time to understand what they're doing and why. It's not just about tools and features; a simulator is just a tool—it won't make design decisions for you any more than a hammer will build a house for you. You need to understand how to use a simulator to identify and debug design problems, or you're going to get stuck.

You need to understand how to use a simulator to identify and debug design problems, or you're going to get stuck.

If you're just getting started, don't "shoot for the moon" in terms of accuracy. Accuracy isn't just about having the right tools—it's about having the expertise, computer resources, and time to use them. Your goal isn't to find 100% of your design issues, it's to take most of the issues off the table so that you can leverage dedicated SI expertise more effectively.

Shaughnessy: That's good.

**Westerhoff:** There are two ways you can waste money. The first way is overdesign—you waste money in manufacturing. You keep wasting money for as long as the design is in production. The second way to waste money is analytical overkill—you waste money in engineering. If you're running a more detailed analysis than is needed to establish that the design will work, you're wasting time, and time is money.

**Shaughnessy:** Do you think we'll see more simulation and analysis tools designed for new users?

**Westerhoff:** I hope so, but I think what we really need is a better bridge between the experts and intermittent users. Chances are, both groups are going to run analysis on the same designs. If the experts can develop useful "best practice" design guidelines for the organization, then the system designers and layout designers can use automated rule checking to ensure the issues are off the table before detailed modeling and simulation begins. I shouldn't have to build a 3M EM model of a board and run analysis just to find out that I have components without decoupling capacitors nearby.

Similarly, any analysis performed by system designers and layout designers should be able to feed directly into the tools the SI experts use. Simulation is a GIGO (garbage in, garbage out) process, and there's lot of work involved to make sure component types and values are tagged properly. The system designers and layout designers are often closer to a particular design than the experts are, they're in a better position to verify that data is correct, and that helps make better use of limited SI expertise.

There's a natural cycle that occurs with SI technology—the issues that are state of the art today become commonplace over time. That means that over time, you can and should be able to take analytical processes that were originally limited to experts, refine and automate them, and then make them accessible to a wider audience. The question then becomes,

what analytical tasks can you make available to what audience? The SI expert crunch isn't going away, so we're going to have to make system designers and layout designers more selfsufficient and find better ways to couple their efforts to the SI experts in their organization.

**Johnson:** This takes us back to the very beginning of the conversation: To put together a comprehensive solution in the current environment, you have to be a simulation expert. That's a huge barrier and another area where engineers will think they have to be an expert in an area that's not their discipline or job.

**Westerhoff:** Absolutely. Most of the time, SI experts are using a collection of tools from different companies to perform a given analysis task. The analysis methodology—what tools get run in what sequence, and how data gets formatted and passed between them—is custom. Parts of the process are usually manual, so you have to pay attention to the details, or the results will be compromised. All of that adds to what you just said: The average system designer will avoid taking on that task.

Since HyperLynx combines DRC/ERC, SI, PI, and 3D EM, we have all the modeling and simulation technology we need to create complete analytical methodologies that don't rely on anyone else's tools. We can define all the analytical steps and data formats, and automate as much of the process as possible, to provide a complete analytical methodology, right out of the box. It's not about having all the tools; it's about having work together with a documented flow. That frees the customer to focus on the thing they care about the most: will their design work, and by how much?

**Shaughnessy:** Are there any myths about simulation out there that you would like to address?

**Westerhoff:** I think some people believe that the only thing that matters with simulation is accuracy, and beyond that all simulators are

equivalent. Accuracy is important, to be sure, but it's not the only thing. There are times when you want a rough answer quickly, times when you want a decent answer and can be a bit more patient, and times when you want the best answer possible and are willing to wait for it. You need a flexible, graduated ability to trade off speed for accuracy.

Saying that the only thing that matters for simulation is accuracy is sort of like saying that the only thing that matters for cars is performance, and that if you only had a great performance car, you'd never need anything else. I've seen people driving Lamborghinis, but I've never seen anyone take their Lamborghini to the lumberyard.

I've seen people driving Lamborghinis, but I've never seen anyone take their Lamborghini to the lumberyard.

**Shaughnessy:** When should an OEM start to consider using simulation or outsourcing to an expert?

**Westerhoff:** I'm going to refer you back to my five points, Andy. You consider it when there's no way forward, when you have failures, when your consultants get too expensive, when overdesign costs mount up, and finally, if you're forward-looking. If we're successful at making simulation easier to use, we'll see those reasons change with time.

**Shaughnessy:** This has been really good, Todd. Maybe we'll catch up in person, if the stars align.

Westerhoff: Always a pleasure, Andy. DESIGN007

## **Growth and Trends in the Thermal Management Market**

## **Sensible Design**

by Jade Bridges, ELECTROLUBE

The ongoing trend for product miniaturisation combined with more modern, higherpowered devices has ensured that reliable thermal management is an essential part of both modern and future electronics design. The LED lighting market is just one example of where thermal management is critical to the durability of the unit. Thermal management products are also offering solutions for greater efficiency in green energy development; photovoltaic inverters, which are known to be particularly sensitive to temperature; connections between the heat-pipe and water storage tank for solar-heating applications; hydrogen fuel cells; and wind power generators.

Is the thermal management market growing now? Yes, it certainly is, due to the everincreasing number of electronic devices and applications entering the market. Demand has risen for higher performance and greater reliability in products with the added requirement of making electronics more discreet to fit into more challenging locations and environments. Let's explore some of the reasons why the market is growing.

#### Is product performance or product reliability deemed most important by manufacturers when producing their products for market?

Both! It depends on the product in most cases. For example, everyone will want their product to perform the best, but each product will have a different expected lifetime. For something with a small turnaround time, i.e., a device that is expected to be updated every one to two years, the performance of that prod-

## **Advanced Technology Capability Does Not Come From Wishful Thinking**

All Facilities Furnished With Cutting-Edge Equipment.

All Facilities Deliver Extraordinary Engineering.

All Facilities Ready To Say "Yes" to The Next Level of Technology.

Advanced Technology | Cycle Time Speed | Knowledgeable People

## 512.548.7435 APCT.com

Printed Circuit Board Solutions

APCT.com

APCT Santa Clara HQ # APCT Anaheim # APCT Orange County # APCT Wallingford # APCT Global 408.727.6442

714.921.0860

714.993.0270

203.269.3311

203.284.1215

uct is most likely going to be the most important factor. It may be competing against many other similar devices on the market and therefore must be both reliable and high performing but with an emphasis towards the latter. For a safety-critical device, you absolutely need reliability. It may not be "all singing and dancing" but as long as it does the job it is intended to do without failure, it will be acceptable. There is usually a trade-off with the properties of any design but remember, by considering thermal management from the start, it should be possible to achieve highly in both areas.

It may not be "all singing and dancing" but as long as it does the job it is intended to do without failure, it will be acceptable.

## Is there a drive for higher and higher levels of thermal conductivity?

Yes, you could say that there is a drive for increased levels of thermal conductivity. However, if you were to investigate each response in detail, thermal conductivity may not actually be the desirable factor engineers are looking for. In all applications, everyone is striving for improved performance and greater efficiency. Simply increasing the level of thermal conductivity alone may not offer you these improvements.

When specifying the thermal conductivity required, it should be based on the end application conditions and requirements. It should also consider the design of the unit/substrate and the application method of the thermal management compound. If the product is not applied correctly—for instance, if air voids are present—then the product cannot offer the full level of thermal dissipation it is capable of.

In general, when you increase the thermal conductivity you must adjust the amount or type of fillers used in the thermal management material and that could impact the viscosity of the product, which in turn affects the overall performance of the product in the end use application. This change may also impact other properties, such as electrical conductivity/ insulation, the material's behaviour in changing temperature conditions, etc. Therefore, while most will say that with electronics becoming more powerful and being used in more challenging environments (and so higher thermal conductivities are needed), each application should be reviewed holistically to make sure that you achieve the best performance from the thermal management material, not just rely on the thermal conductivity value alone.

#### Heat generation rises in line with miniaturisation and the desire for higher performing components—what are the solutions?

Look at the design of the unit/PCB; are there any ways in which heat could be distributed more effectively? For example, if all heat-generating components are now in one area and close together, could they be relocated? This sounds simple to do but in practice it is not always possible. Other ways to effectively dissipate the heat away from certain areas is to ensure you have the best thermal interface material for your application. That means checking the thermal resistance at the interface, or more simply, checking the temperature of components or areas of the board. When you have this starting information, you can look at ways to improve heat dissipation by adjusting the thermal interface material used, for example. This could be moving to a product with higher thermal conductivity, however, make sure it can still be applied correctly to enable it to perform as expected.

As well as looking at the interface materials used, you could also look into the gaps around the board. Are there any areas where hot air could gather whilst the unit is in operation? Does the outer case offer any heat dissipation, i.e., is it made of metal? If so, could you utilise a gap-filling product to help remove these localised pockets of air? There are many ways to reduce heat dissipation but again it is important to look at the unit/PCB as a whole, as an action taken in one area of the board may lead to issues elsewhere.

## What new trends are expected in global thermal management?

Due to developments in the electronics industry, the introduction of smaller and smarter products is increasing. These advancements in the industry have led to an increased need for innovative thermal management technologies to improve system performance and reliability by eliminating the heat generated by devices. Trends driving growth in this market include the increasing popularity of smartphones and tablets, which have seen considerable growth in the past decade. Due to mounting sensitivity toward weight and price, the need for advanced thermal management solutions is increasing.

Artificial intelligence (AI) is growing rapidly for the next generation of smartphone, smart home device, and smart speaker categories. This is expected to drive the thermal management technologies market further.

Increasing awareness of environmental issues combined with potential performance advantages is propelling the adoption of electric vehicles and a more widely available charging infrastructure, both of which rely heavily on thermal management predominantly for increasing the reliability and performance of battery systems. Also, the increasing adoption of renewable energy resources is a major factor driving the thermal management market.

Due to escalating industrialization across the world, demand has risen for continuous power supplies, which has positively impacted the growth of the thermal management market to ensure maximum reliability. For instance, capacitors are used to temporarily store electricity where required, or in off-grid applications batteries may be required to store power for more widespread use. In such cases, these electronic devices will require protection from the elements but will also be required to operate at higher temperatures and offer some form of thermal dissipation, due to the heat emitted during operation. Depending on the design, thermal management products will be used to help dissipate heat away from devices to maintain efficient, continual power.

Depending on the design, thermal management products will be used to help dissipate heat away from devices to maintain efficient, continual power.

I hope the points covered this month have been helpful and please look for my next column, where I'll be covering more issues on thermal management to get the best heat protection for your circuitry requirements. In the meantime, please contact me if you have any questions. We also have numerous technical resources available for your interest, such as how-to videos on our youtube channel, and articles and blog stories on newly updated, application-focused website at www.electrolube.com. DESIGN007

Jade Bridges is global technical support manager at Electrolube. To read past columns from Electrolube, click here. Download your free copy of Electrolube's book, *The Printed Circuit Assembler's*

*Guide to... Conformal Coatings for Harsh Environments,* and watch the micro webinar series "Coatings Uncoated!"

## **Alternatives to Simulation**

Feature Article by Dan Beeker NXP SEMICONDUCTORS

We are living in an age where the demands on electronic product designs are constantly evolving. The IC technology and operating speeds continue to pose significant challenges for teams as they work to develop their products. The increased transistor switching speeds and less forgiving compliance standards make signal integrity and electro-magnetic compliance more difficult to achieve. The status quo seems to have become, "We expect to fail EMC testing."

What can be done to increase the likelihood of compliance, and proper function? In some cases, the engineering community looks to simulation as a method of evaluating the PCB design. There are certainly a number of powerful tools available, but they are usually expensive and difficult to use properly. These tools are only of value if the transmission lines are not broken. The simulated results often differ from the measured behaviors, forcing model tweaks and lost time. In most cases, you have an incomplete model and inaccurate measurements, which even when reconciled, do not reflect the real behaviors of the design. It is nearly impossible to get good measurements for this purpose. The probes will affect the signal, as does the location in the transmission line where the measurement is taken. Many teams just do not have the bandwidth or expertise to achieve success using this process.

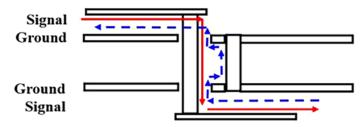

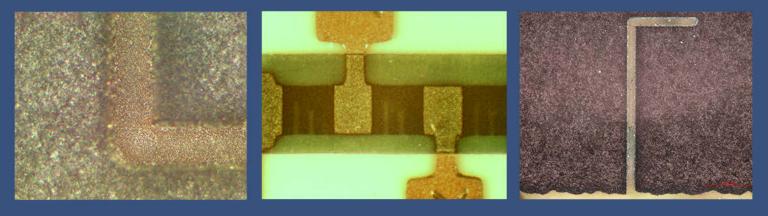

The fundamental issue is that most simulation tools are not capable of evaluating broken transmission lines. (I say "most" because I am not intimately familiar with all of them.) A broken transmission line is a signal or power conductor that is not one dielectric away from ground. If a signal or power conductor is not directly adjacent to a continuous dielectric bounded by a continuous ground conductor, the EM fields do not stay where the design requires. The field will fill the space between

Figure 1: If the return plane is split, the field must fill the space between the signal trace and the ground copper. (Image courtesy of Rick Hartley, consultant)

## cādence°

## Full-Wave 3D FEM Extraction and Analysis of Large and Complex Packages and PCBs up to 10X Faster

Attend our webinar to learn and apply the latest innovations in full-wave 3D model extraction and analysis of your next-gen system design

**REGISTER NOW**

**UNLEASH IMAGINATION**

KERTERESTERETERESTERE

www.cadence.com

the signal conductor and the ground conductor that connects to the power source for the PCB.

The more conductors and dielectrics that are between the signal in question and its ground, the more impact on signal integrity and EMC. There are just not enough nodes in the models. It would require characterizing every change in the transmission line geometry, for not only the signal trace in question, but the other nearby traces and the power supplies for the ICs involved. Once a trace crosses a split in the ground plane, the space involved in the signal transmission expands to include the divergent path of the continuous ground conductor. This increases the time it takes to establish the signal voltage, requiring more wave cycles to achieve the signal levels. Each wave cycle increases crosstalk and possible radiated emissions, which occur at every wavefront. Every other signal crossing the split will also have an expanded space to fill. These signals will then share the space and affect the voltage for each signal. If a power supply is not properly designed, signal integrity is compromised for all the signals using that supply. If a signal is compromised, it affects not only that signal, but other signals in the adjacent areas of the PCB.

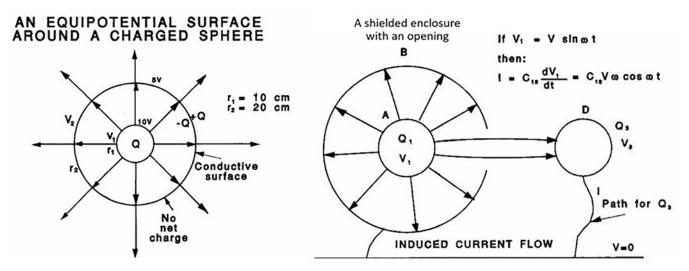

Having a proper understanding of PC board design and how to totally contain EM fields will minimize or negate the need for simulation. We have to start with a different understanding of how electronic circuits function. Containing EM fields requires three things: two conductors separated by a space. If one of these components is missing, the EM field will behave in well-defined ways. If there is only one conductor, such as a sphere, with no hole in it, any field contained inside the sphere cannot escape. If there is only one conductor and a space, the field will not be contained. If there is no space between two different conductors, such as between power vias next to each other, then there is no field in that space.

Next, it is important to understand that you only get three components to use in managing the fields: conductors, spaces, and switches. ICs are just giant switch arrays. Finally, there are only three things you can do with EM fields: Store them, move them, or convert them into kinetic energy. This is not rocket science. Using this perspective is crucial in achieving signal integrity and EMC goals. It is all about the space.

Empirical analysis of the PCB design can be a good first step in achieving signal integrity and EMC compliance. The first thing you

Figure 2: Remember: If you have one conductor, such as a sphere, with no hole in it (2a), any EM field contained inside the sphere cannot escape. If there is only one conductor and a space (2b), the field will not be contained. (Images courtesy of Ralph Morrison, consultant)

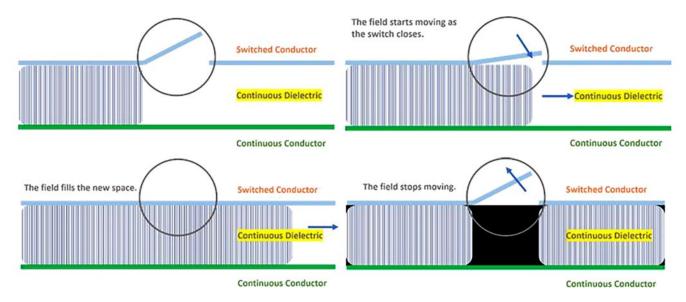

Figure 3: Images depicting the movement of an EM field as a switch closes. There are only three things that you can do with EM fields: Store them, move them, or convert them into kinetic energy.

need to understand is that the EM energy used in the circuit travels in the dielectric, not the conductors. The PCB conductors are used to create the boundaries for the spaces where the EM fields will go. Managing these spaces starts with the board stackup. If at all possible, there needs to be a solid ground plane between each pair of signal/power layers. These form a triplet (signal-ground-signal) or a paired dielectric, which allows routing between the two conductor layers to be done with only the signal via. The opening around the via in the ground plane provides the connection between the top and bottom dielectric layers. For example, in a four-layer PCB, if layer two is ground, then layers one and three form the boundaries for the paired dielectrics between them. In this case, layer four is not adjacent to the ground plane, and must be treated as if it were single layer board. Each signal trace needs to be routed next to a ground trace or ground flood area. When connecting layer

When moving signals between layers, route on either side of the same plane, as much as possible!

When moving signals *between two different ground planes*, use a transfer or "ground transition" via very near the signal via.

Figure 4: Moving EM signals often involves some clever routing and via placement, but it's not rocket science. (Images courtesy of Rick Hartley, consultant)

four to layer one or layer three, a ground transition via is required, to connect the dielectric between the traces on layer four in the Z-axis to the dielectrics in the triplet formed by layers one, two and three. This pattern must be repeated to create a solid foundation for EM field control.

A six-layer board stack is extremely powerful, providing two sets of paired dielectrics and four routing layers that form good transmission lines. Again, care must be taken when routing between these paired dielectrics, to connect the spaces in the Z-axis. The plumbing must be intact from the source of the energy to the load, in all three dimensions. Some signals can never be compromised. The crystal circuit and power supply are two very good examples of this. The one dielectric rule must always be enforced for these signals, with the traces routed over continuous ground copper on an adjacent layer or co-planar ground copper (a poor second choice).

Analysis of the PDN is the next step on the road to signal integrity and compliance. In the case of the power supply, not only is the one dielectric rule inviolate, but the capacity of the dielectric to carry EM fields must be adequate to supply the needed energy for the devices connected to it. This is not achieved by increased copper weight, but by having an impedance that matches the need. Thinner dielectrics, wider conductors, or multiple parallel transmission lines are required for good power distribution, as are properly sized and placed capacitors in the PDN. The capacity of the power supply transmission lines is critical.

If you need five amps, you need the dielectric that has the capacity to deliver this much energy. Current flow is a measure of the amount of EM field energy passing through the dielectric. Five amps is five coulombs of energy per second, much like the idea of water flow in a pipe, measured in gallons per minute. If you need five gallons of water per second, a one-gallon-per-minute pipe will not do the job. The same is true for the PDN. If you need five amps, you must provide the spaces that can carry that much energy. It is the dielectric that is the key here, not the conductors. Adding more copper weight does not increase the capacity of the dielectric. Again, only reducing the dielectric thickness, increasing the copper conductor surface area (trace width) or adding more parallel transmission lines, will increase the capacity of the PDN.

In conclusion, with proper EM field planning, you can often avoid having to simulate a PCB design. The first line of defense for achieving good signal integrity and compliance is to review the PCB design. Look for areas where the one dielectric rule was violated. Start with the board stack. Are there paired dielectrics? Are they connected to the other layers properly? Are there ground transition vias where needed? This is especially important in circuits such as SMPS designs, where the components are placed on both sides of the board. Properly connecting the top dielectric, adjacent to the top layer, to the bottom dielectric is critical. Each power via needs a ground transition via. Does the PDN provide adequate capacity and properly placed components? In many cases, parallel Z-axis transmission lines are needed to ensure there is enough capacity to allow the energy to move between components.

As Ralph Morrison always said, "Buildings have walls and halls. People travel in the halls, not the walls. Circuits have traces and spaces. Energy and signals travel in the spaces, not the traces." Design the spaces, by using the traces. To help you all remember this, enjoy "All About the Space," a remake of the Meghan Trainor song, featuring my daughter Breezy Beeker on vocals. DESIGN007

Dan Beeker is a senior principal engineer at NXP Semiconductor.

# Need help finding the right people for your team?

DB Management knows that finding the right people can be like looking for a needle in a haystack. We can streamline your hiring process with pre-qualified candidates.

Engineering · Management · Sales & Marketing

### Click here to get started

🔇 207-649-0879 🖾 danbbeaulieu@aol.com

### Jan Pedersen: Getting Into Ultra-HDI With IPC Committees

Interview by Andy Shaughnessy I-CONNECT007

I recently spoke with Elmatica's Jan Pedersen about winning the IPC Dieter Bergman Fellowship Award this year, as well as his work on a variety of IPC committees. Jan, a regular PCB007 columnist, explained how he and a group of committee members are now exploring ways to bring 1-mil traces into the mainstream, and the need to bring more traceability into automotive and medical PCB standards.

**Andy Shaughnessy:** Jan, congratulations on being awarded the IPC Dieter Bergman Fellowship Award.